VRIJE UNIVERSITEIT BRUSSEL

#### FACULTEIT WETENSCHAPPEN EN BIO-INGENIEURSWETENSCHAPPEN DEPARTEMENT NATUURKUNDE

# The Upgraded Outer Tracker for the CMS Detector at the High Luminosity LHC, and Search for Composite Standard Model Dark Matter with CMS at the LHC

JARNE DE CLERCQ

PROMOTER PROF. DR. STEVEN LOWETTE

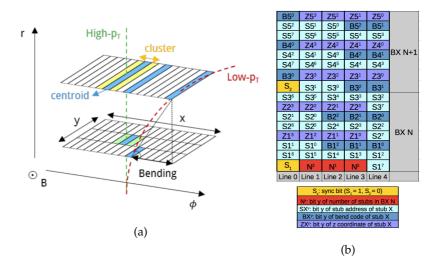

Proefschrift ingediend met het oog op het behalen van de academische graad van Doctor in de Wetenschappen

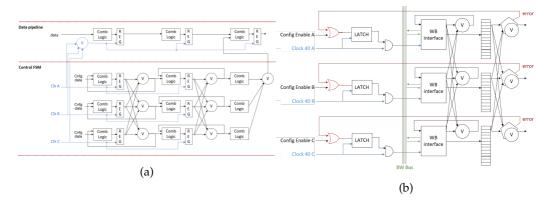

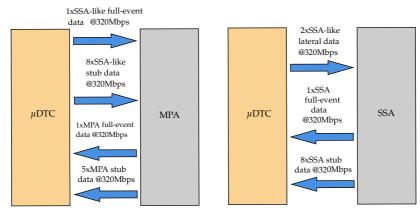

January 2020

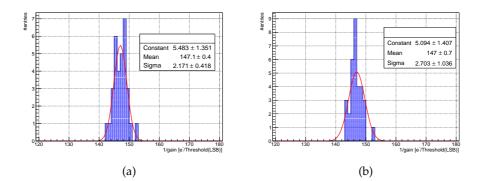

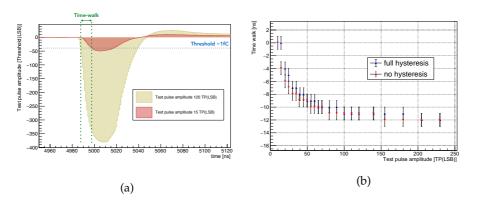

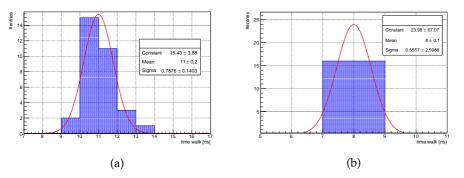

Doctoral examination commission:

- Prof. Dr. Krijn De Vries (Vrije Universiteit Brussel, *secretary*) Prof. Dr. Jorgen D'Hondt (Vrije Universiteit Brussel, *chair*) Prof. Dr. Steven Lowette (Vrije Universiteit Brussel, *supervisor*) Prof. Dr. Nadia Pastrone (INFN, Torino) Prof. Dr. ir. Gerd Vandersteen (Vrije Universiteit Brussel)

- Prof. Dr. Pascal Vanlaer (Université Libre de Bruxelles)

Cover illustration: Patrick De Clercq

Printed by Crazy Copy Center Productions VUB Pleinlaan 2, 1050 Brussel Tel : +32 2 629 33 44 crazycopy@vub.ac.be www.crazycopy.be ISBN: 9789493079571 NUR: 924, 926, 987

©2020 Jarne De Clercq

All rights reserved. No parts of this book may be reproduced or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the author.

# Contents

| Sı | ummary                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                    | ix                                                                                      |

|----|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Sa | menvatti                                                                | ng                                                                                                                                                                                                                                                                                                                                                                                                                 | xi                                                                                      |

| A  | uthor's Co                                                              | ontribution                                                                                                                                                                                                                                                                                                                                                                                                        | xiii                                                                                    |

| I  | Setting                                                                 | g the Stage                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                       |

| 1  | Preambl                                                                 | le                                                                                                                                                                                                                                                                                                                                                                                                                 | 3                                                                                       |

| 2  | 2.1 In<br>2.2 Th<br>2.3 Th<br>2.4 Da<br>2.4<br>2.4<br>2.4<br>2.4<br>2.4 | 2       Evidence for dark matter         .3       Dark matter candidates                                                                                                                                                                                                                                                                                                                                           | <b>5</b><br>5<br>6<br>9<br>9<br>9<br>11<br>13<br>13                                     |

| 3  | 3.1 In<br>3.2 Pa<br>3.2<br>3.2<br>3.2<br>3.2<br>3.2<br>3.2<br>3.3 Cl    | 2Electron interactions with matter.3Photon interactions with matter.4Heavy neutral particle interactions with matter.4Heavy neutral particle interactions with matter.4Heavy neutral particle interactions with matter.4Interactions with matter.5Discon based detectors for tracking.1Introduction.1Introduction.2Silicon doping and the pn-junction.3Layout and operation of a position sensitive silicon sensor | <b>15</b><br>15<br>15<br>15<br>18<br>18<br>19<br>19<br>20<br>20<br>20<br>20<br>22<br>23 |

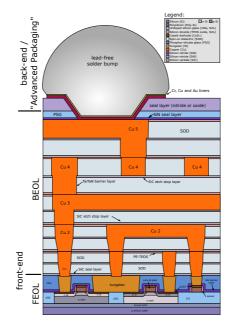

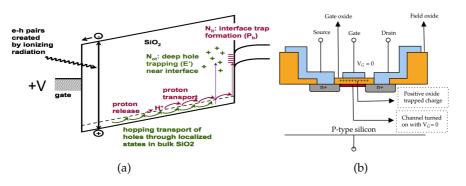

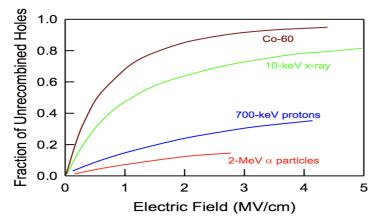

|    | 3.5 In<br>3.6 Re                                                        | tegrated circuits                                                                                                                                                                                                                                                                                                                                                                                                  | 24<br>25<br>27<br>27                                                                    |

|   |     | 3.7.2 | Total ionizing dose                              | 28         |

|---|-----|-------|--------------------------------------------------|------------|

|   |     |       | 3.7.2.1 Introduction                             | 28         |

|   |     |       | 3.7.2.2 Total ionizing dose mechanism            | 28         |

|   |     |       | 3.7.2.3 Total ionizing dose hardening techniques | <u>2</u> 9 |

|   |     |       | 3.7.2.4 Total ionizing dose testing 2            | <u>2</u> 9 |

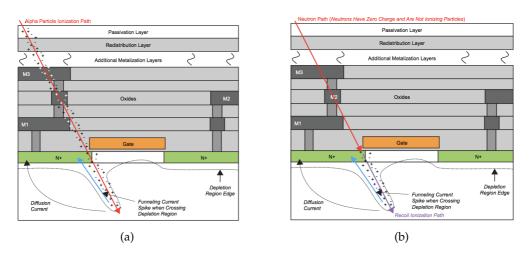

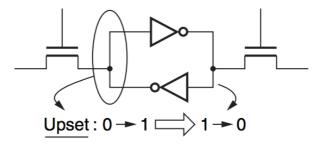

|   |     | 3.7.3 | Single-event effects                             | 30         |

|   |     |       | 3.7.3.1 Introduction                             | 30         |

|   |     |       | 3.7.3.2 Single-event upset mechanism             | 30         |

|   |     |       |                                                  | 32         |

|   |     |       | 3.7.3.4 Single-event upset testing 3             | 33         |

|   | 3.8 | Sumi  |                                                  | 33         |

| 4 | The | LHC a | nd the CMS Experiment 3                          | 35         |

|   | 4.1 |       |                                                  | 35         |

|   | 4.2 |       |                                                  | 35         |

|   | 4.3 |       | CMS experiment                                   | 38         |

|   |     | 4.3.1 |                                                  | 38         |

|   |     | 4.3.2 |                                                  | <b>1</b> 0 |

|   |     |       |                                                  | <b>1</b> 0 |

|   |     |       | •                                                | <b>1</b> 1 |

|   |     | 4.3.3 |                                                  | 14         |

|   |     | 4.3.4 |                                                  | 45         |

|   |     | 4.3.5 |                                                  | <b>1</b> 6 |

|   | 4.4 | The H |                                                  | <b>1</b> 7 |

|   | 4.5 |       |                                                  | 18         |

|   | 4.6 |       | 10                                               | 52         |

|   |     |       |                                                  |            |

## II The Upgraded Outer Tracker for the CMS Detector at the High Luminosity LHC 53

| 5 | The |                      |           | uter Tracker                                      |     |   | 55 |

|---|-----|----------------------|-----------|---------------------------------------------------|-----|---|----|

|   | 5.1 |                      |           |                                                   |     |   | 55 |

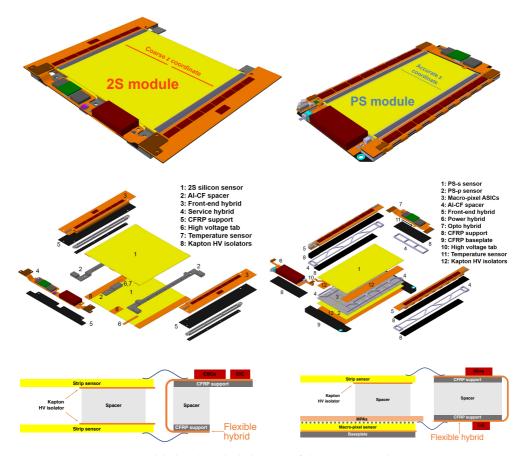

|   | 5.2 | $p_{\rm T}  {\rm m}$ | odule con | cept and design                                   |     |   | 56 |

|   |     | 5.2.1                |           | nodule                                            |     |   | 59 |

|   |     | 5.2.2                | The 2S n  | nodule                                            |     |   | 59 |

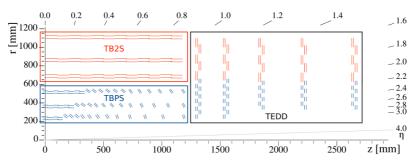

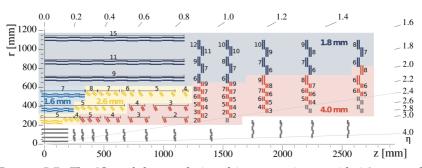

|   | 5.3 | Oute                 | r Tracker | geometry                                          |     |   | 60 |

|   | 5.4 |                      |           | · · · · · · · · · · · · · · · · · · ·             |     |   | 60 |

|   | 5.5 |                      |           | Cs                                                |     |   | 61 |

|   |     | 5.5.1                |           | nalities between the SSA, MPA, CBC and CIC ASICs. |     |   | 63 |

|   |     | 5.5.2                |           | chip                                              |     |   | 65 |

|   |     |                      | 5.5.2.1   | Introduction                                      |     |   | 65 |

|   |     |                      | 5.5.2.2   | SSA front-end                                     |     |   | 65 |

|   |     |                      | 5.5.2.3   | SSA sampling logic                                |     |   | 66 |

|   |     |                      | 5.5.2.4   | SSA stub data path and format                     |     |   | 67 |

|   |     |                      | 5.5.2.5   | SSA full-event data path and format               |     |   | 67 |

|   |     | 5.5.3                | 0.0.2.0   |                                                   |     |   | 68 |

|   |     | 5.5.5                | 5.5.3.1   | A chip                                            |     |   | 68 |

|   |     |                      | 0.0.0.1   | Introduction                                      |     |   |    |

|   |     |                      | 5.5.3.2   | MPA front-end                                     | ••• | • | 68 |

|   |            |                | 5.5.3.3 MPA sampling logic                               | 69                |

|---|------------|----------------|----------------------------------------------------------|-------------------|

|   |            |                | 5.5.3.4 MPA stub data path and format                    | 70                |

|   |            |                | 5.5.3.5 MPA full-event data path and format              | 70                |

|   |            | 5.5.4          | MPA and SSA single-event effect tolerant design strategy | 72                |

|   |            | 5.5.5          | The CBC chip                                             | 73                |

|   |            |                | 5.5.5.1 Introduction                                     | 73                |

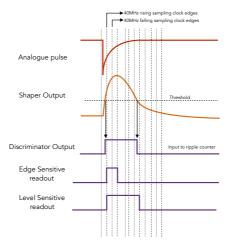

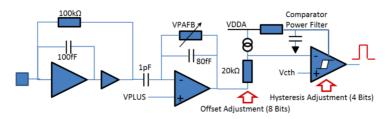

|   |            |                | 5.5.5.2 CBC front-end                                    | 73                |

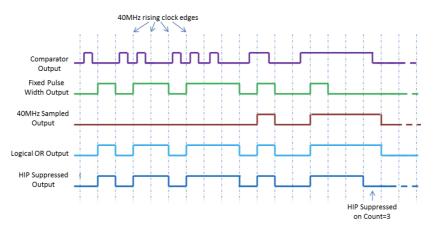

|   |            |                | 5.5.5.3 CBC sampling logic                               | 74                |

|   |            |                | 5.5.5.4 CBC stub data path and format                    | 76                |

|   |            |                | 5.5.5.5 CBC full-event data path and format              | 77                |

|   |            |                | 5.5.5.6 The CBC2 chip                                    | 78                |

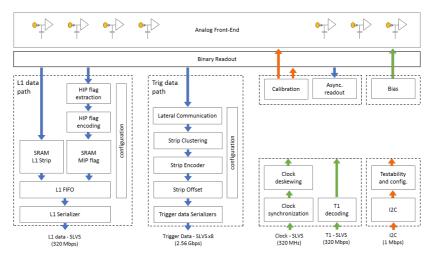

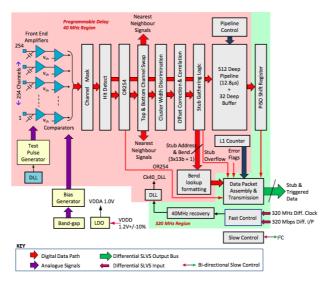

|   |            | 5.5.6          | The CIC chip                                             | 78                |

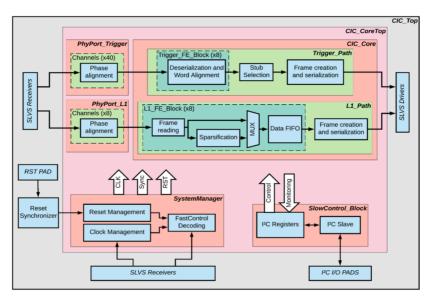

|   |            | 0.0.0          | 5.5.6.1 Introduction                                     | 78                |

|   |            |                | 5.5.6.2 Phy ports                                        | 79                |

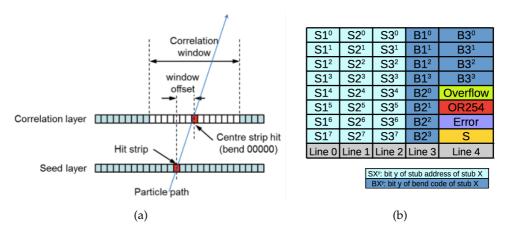

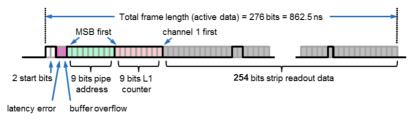

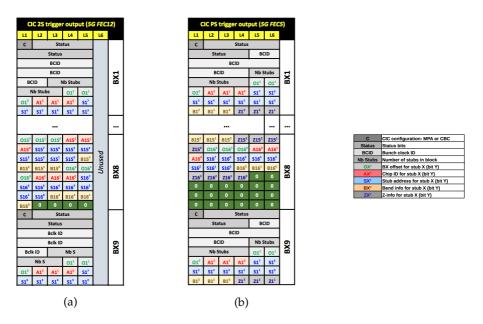

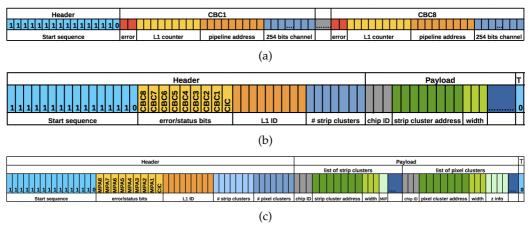

|   |            |                | 5.5.6.3 CIC stub data path and formats                   | 80                |

|   |            |                | 5.5.6.4 CIC full-event data path and formats             | 82                |

|   |            |                | 1                                                        | 83                |

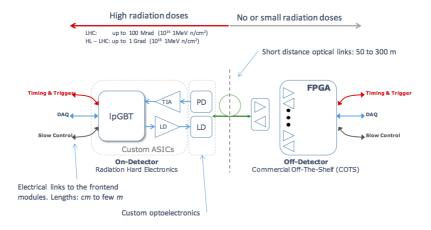

|   |            | 5.5.7          | 1                                                        | 83                |

|   | ΕC         |                | The optical link                                         |                   |

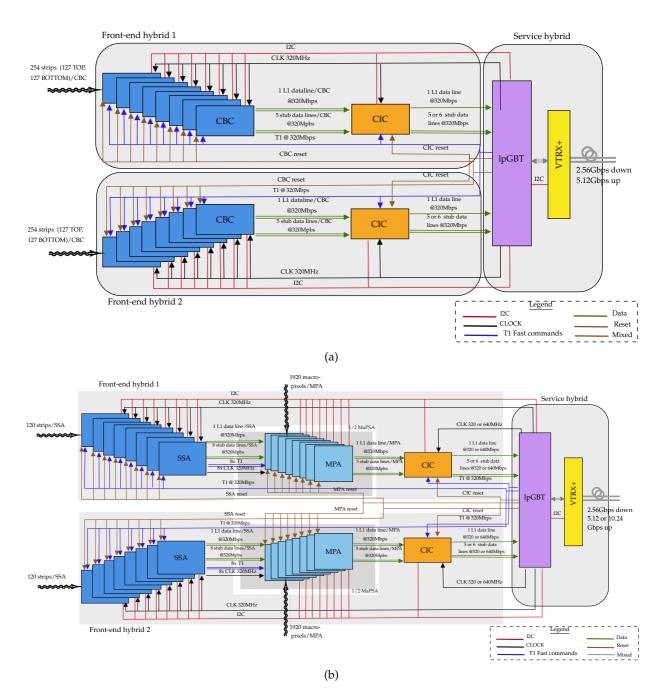

|   | 5.6        |                | odule data path                                          | 85                |

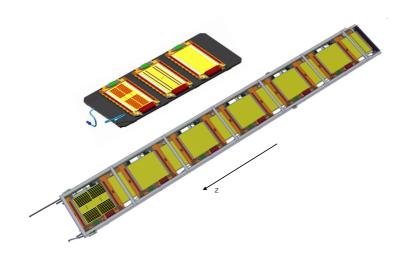

|   | 5.7        |                | ule assembly and testing during production               | 86                |

|   | 5.8        |                | , trigger and control system                             | 88                |

|   | 5.9        |                | ack finding                                              | 88                |

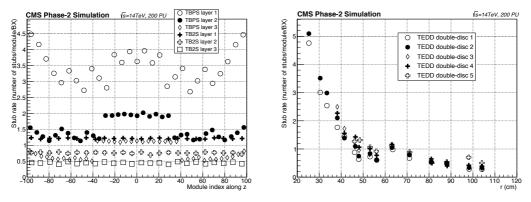

|   | 5.10       |                | e-2 tracker expected performance                         | 88                |

|   | 5.11       | Sum            | mary                                                     | 89                |

| 6 | Firm       | ware I         | Development for Phase-2 Tracker Prototypes               | 93                |

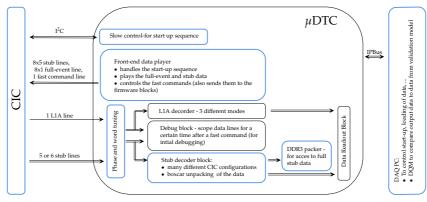

| U | 6.1        |                | duction                                                  | 93                |

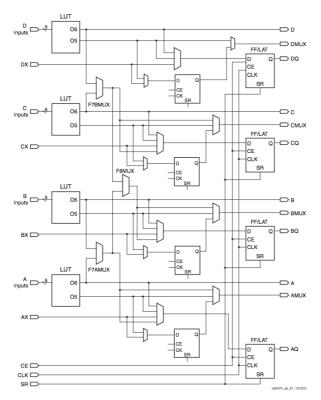

|   | 6.2        |                | As                                                       | 93                |

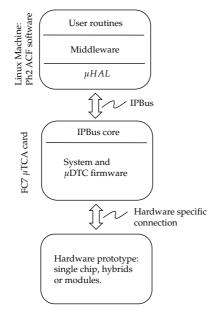

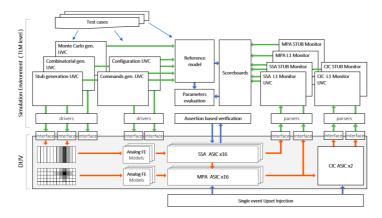

|   | 6.3        |                | e of the $\mu$ DTC test-bench                            | 94                |

|   | 6.4        |                |                                                          | 96                |

|   | 0.4        | 6.4.1          | The $\mu$ TCA standard                                   | 96                |

|   |            | 6.4.2          | The IPbus protocol $\ldots$                              | 90<br>97          |

|   |            | 6.4.2<br>6.4.3 | The FC7 AMC card                                         | 97<br>97          |

|   |            | 6.4.3<br>6.4.4 |                                                          | 97<br>98          |

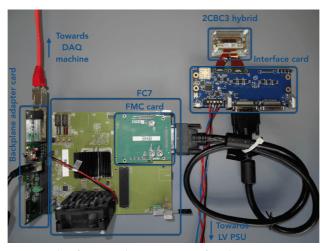

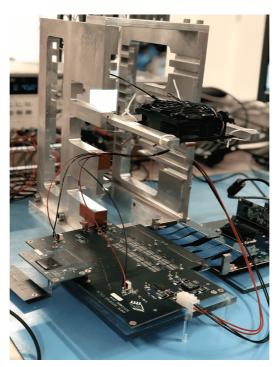

|   | 6 5        |                | Example of a typical µDTC set-up                         | 98<br>99          |

|   | 6.5        | ,              |                                                          | 99<br>99          |

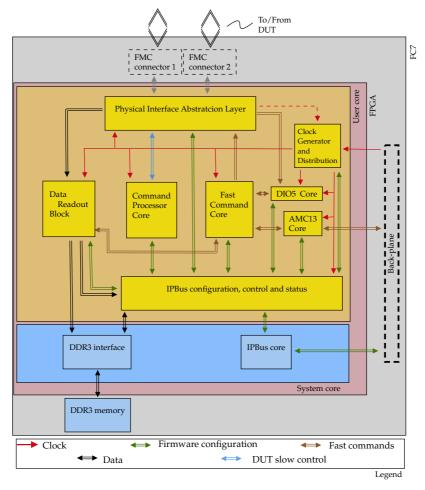

|   |            | 6.5.1          | Introduction                                             |                   |

|   |            | 6.5.2          | The Physical Interface Abstraction Layer                 | 101               |

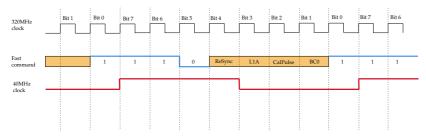

|   |            |                | 6.5.2.1 Fast commands                                    | 101               |

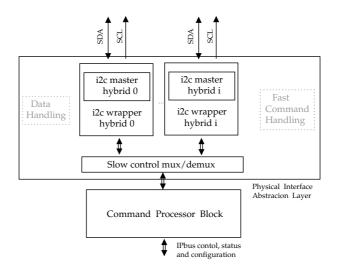

|   |            |                | 6.5.2.2 Slow control                                     | 101               |

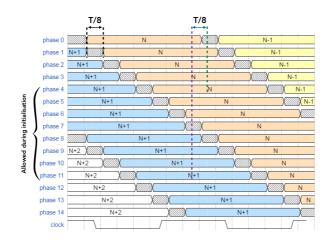

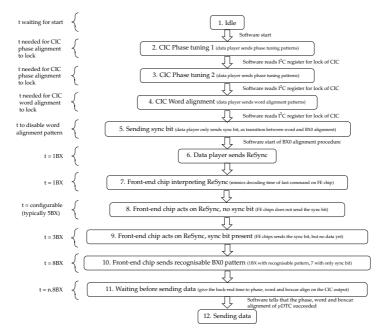

|   |            |                | 6.5.2.3 Phase tuning of the incoming data                | 102               |

|   |            | . = -          | 6.5.2.4 Front-end data acquisition                       | 102               |

|   |            | 6.5.3          | Data Readout Block                                       | 103               |

|   |            | 6.5.4          | Command Processor Block                                  | 104               |

|   |            | 6.5.5          | Fast Command Block                                       | 104               |

|   |            | < <            |                                                          |                   |

|   |            | 6.5.6          | Firmware testing                                         | 105               |

|   | 6.6<br>6.7 | Sum            | Firmware testing                                         | 105<br>106<br>106 |

vi

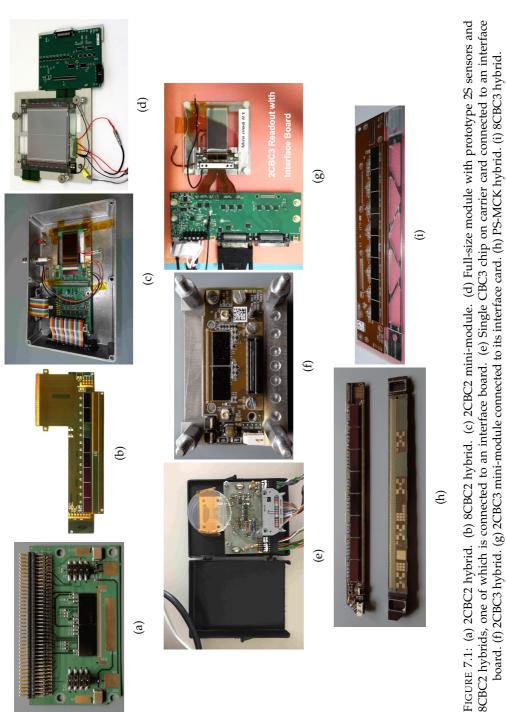

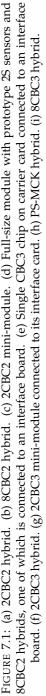

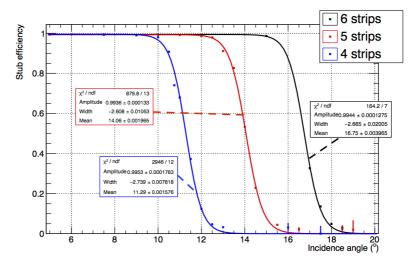

| 7 | 2S P | rototyp | be Testing                                                  | 107 |

|---|------|---------|-------------------------------------------------------------|-----|

|   | 7.1  | Intro   | duction                                                     | 107 |

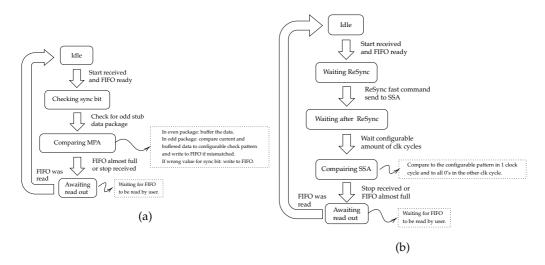

|   | 7.2  |         | fic firmware development for 2S based systems               | 107 |

|   |      | 7.2.1   | Introduction                                                | 107 |

|   |      | 7.2.2   | Use cases                                                   | 107 |

|   | 7.3  | CBC3    | 3 test pulse injection testing                              | 109 |

|   |      | 7.3.1   | Introduction                                                | 109 |

|   |      | 7.3.2   | Procedure                                                   | 110 |

|   |      | 7.3.3   | Results                                                     | 110 |

|   | 7.4  |         | nary                                                        | 116 |

|   | 7.5  |         | or's contribution                                           | 116 |

|   | 1.0  | 11001   |                                                             | 110 |

| 8 | PS F | rototyp | oe Testing                                                  | 117 |

|   | 8.1  | Intro   | duction                                                     | 117 |

|   | 8.2  | Speci   | fic firmware development for PS based systems               | 117 |

|   |      | 8.2.1   | Introduction                                                | 117 |

|   |      | 8.2.2   | MPA/SSA debug firmware and PS specific test features        | 117 |

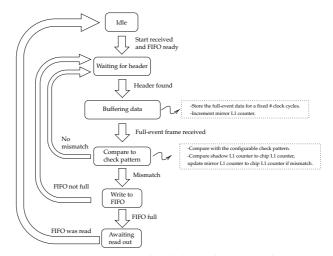

|   |      | 8.2.3   | MPA/SSA DAQ firmware                                        | 119 |

|   |      | 8.2.4   | Use cases                                                   | 120 |

|   | 8.3  |         | e chip testing                                              | 120 |

|   |      | 8.3.1   | MPA                                                         | 122 |

|   |      | 8.3.2   | SSA                                                         | 122 |

|   | 8.4  |         | and SSA single-event upset testing                          | 123 |

|   | 0.1  | 8.4.1   | Introduction                                                | 123 |

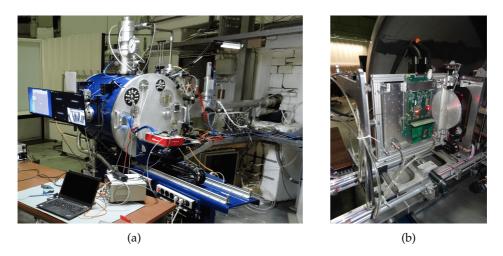

|   |      | 8.4.2   | Heavy ion facility                                          | 123 |

|   |      | 8.4.3   | Test set-up                                                 | 123 |

|   |      | 8.4.4   | SEU cross section calculation                               | 127 |

|   |      | 8.4.5   | Results                                                     | 129 |

|   |      | 0.4.5   | 8.4.5.1 SEU triggered configuration and control upsets      | 129 |

|   |      |         | 8.4.5.2 SEU cross section and bit upset rates on data paths | 129 |

|   | 8.5  | Singl   | e-MaPSA test beam                                           | 135 |

|   | 0.5  | 8.5.1   |                                                             | 135 |

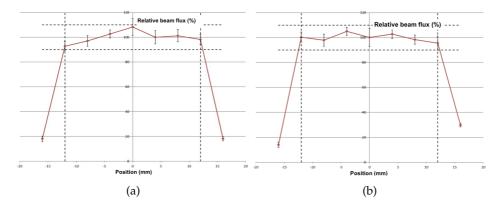

|   |      | 8.5.2   | Beam area                                                   | 135 |

|   |      | 0.3.2   |                                                             | 135 |

|   |      |         | 8.5.2.1         Beam parameters                             | 135 |

|   |      | 0 5 2   | 1                                                           | 135 |

|   |      | 8.5.3   | Single-MaPSA                                                | 136 |

|   |      | 8.5.4   | Single-MaPSA set-up                                         |     |

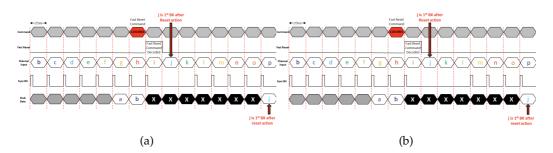

|   |      | 8.5.5   | MPA data streams                                            | 137 |

|   |      | 8.5.6   | Commissioning of the single-MaPSA                           | 138 |

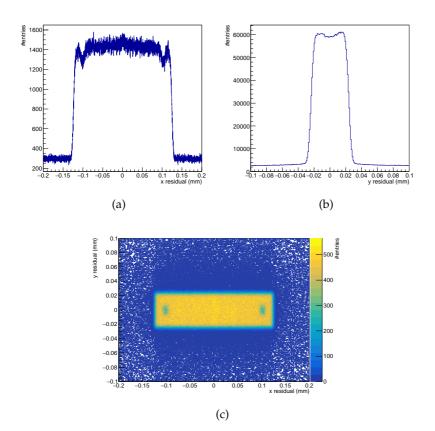

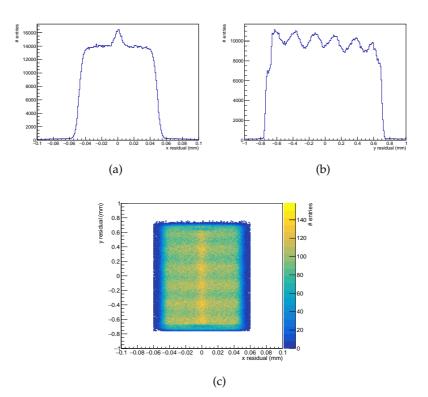

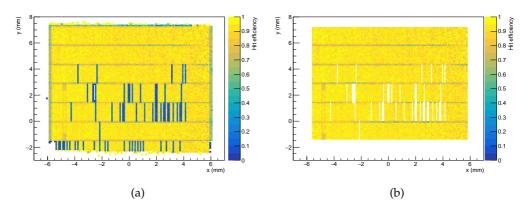

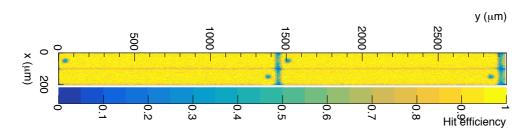

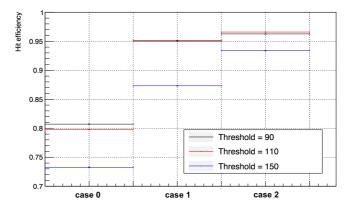

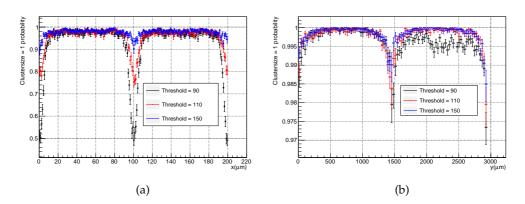

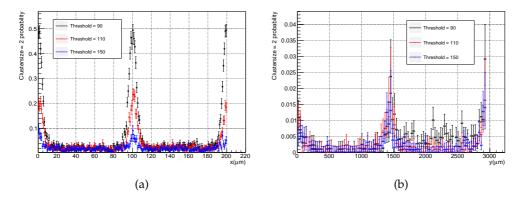

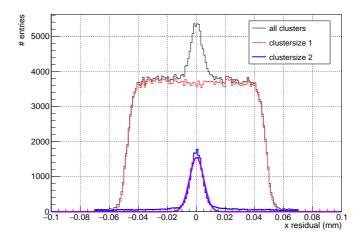

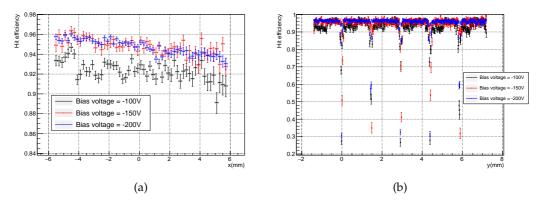

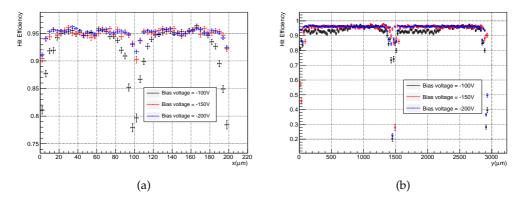

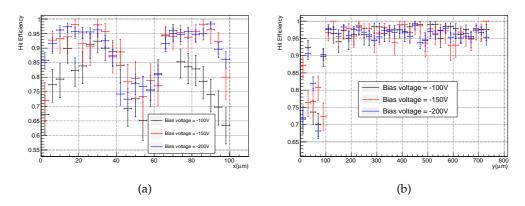

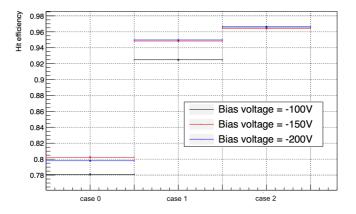

|   |      | 8.5.7   | Results                                                     | 140 |

|   |      |         | 8.5.7.1 Assembly #1 and #2: DUT only                        | 141 |

|   |      |         | 8.5.7.2 Assembly #1: combined results of threshold scans    | 145 |

|   |      |         | 8.5.7.3 Assembly #1: threshold scan                         | 149 |

|   |      |         | 8.5.7.4 Assembly #1: bias scan                              | 155 |

|   |      | 6       | 8.5.7.5 Assembly #2                                         | 159 |

|   | 8.6  |         | mary                                                        | 159 |

|   | 8.7  | Auth    | or's contribution                                           | 160 |

| 9 | CIC        | 1 Relat | ed Testing                             | 163 |

|---|------------|---------|----------------------------------------|-----|

|   | 9.1        | Intro   | duction                                | 163 |

|   | 9.2        |         | stand-alone testing                    | 163 |

|   |            | 9.2.1   | Introduction                           | 163 |

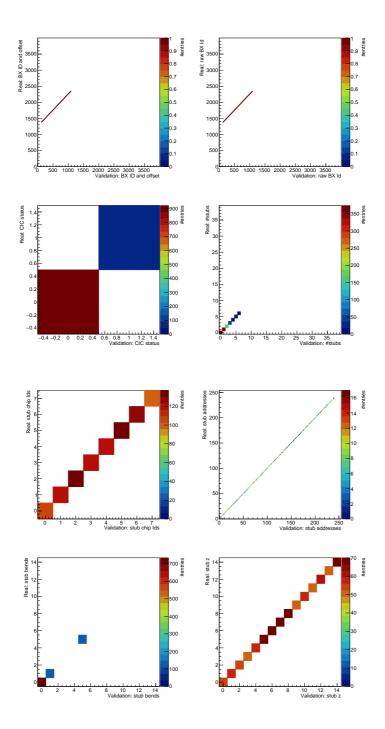

|   |            | 9.2.2   | Reference model                        | 165 |

|   |            | 9.2.3   | Front-end data player                  | 166 |

|   |            | 9.2.4   | CIC decoder blocks                     | 168 |

|   |            | /       | 9.2.4.1 Full-event data                | 168 |

|   |            |         | 9.2.4.2 Stub data                      | 170 |

|   |            | 9.2.5   | Data quality monitoring                | 174 |

|   |            | 9.2.6   | Data processing test results           | 175 |

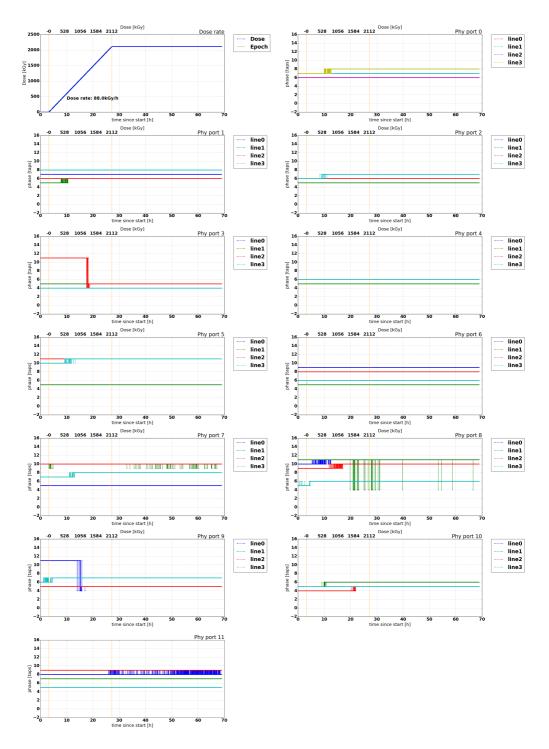

|   |            | 9.2.7   | Irradiation testing                    | 176 |

|   |            | ).2.1   | 9.2.7.1 EP-ESE irradiation system      | 176 |

|   |            |         | •                                      | 176 |

|   |            |         | ······································ | •   |

|   | ~ <b>^</b> |         | 9.2.7.3 Results                        | 178 |

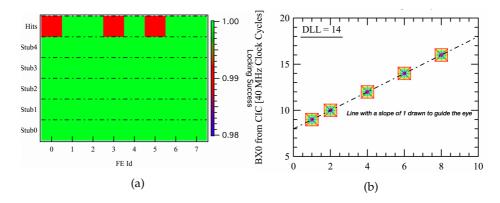

|   | 9.3        |         | C3 + CIC1 testing                      | 180 |

|   |            | 9.3.1   | Introduction                           | 180 |

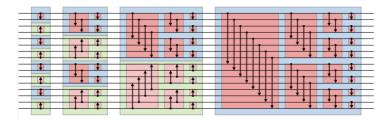

|   |            | 9.3.2   | Running 8CBC3 + CIC1                   | 182 |

|   | 9.4        | Sumi    | mary                                   | 184 |

|   | 9.5        |         | or's contribution                      | 185 |

# **III** Search for Composite Standard Model Dark Matter with CMS at the LHC

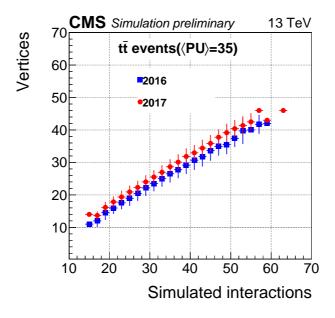

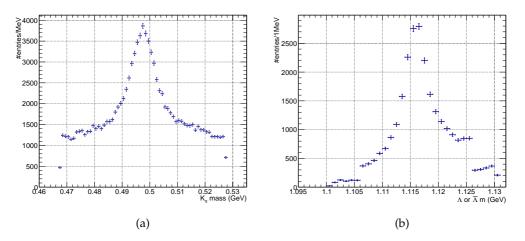

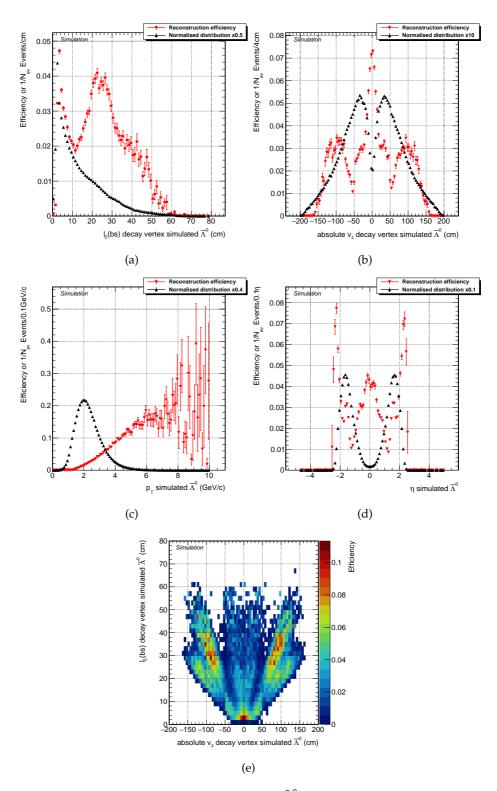

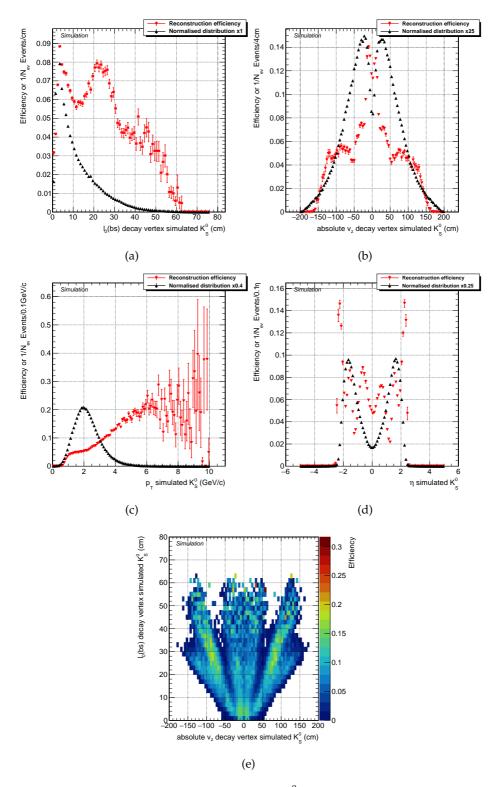

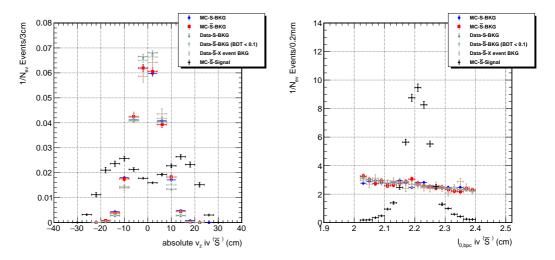

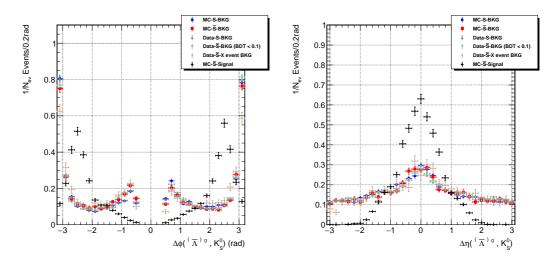

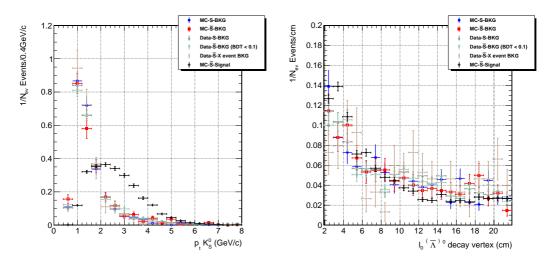

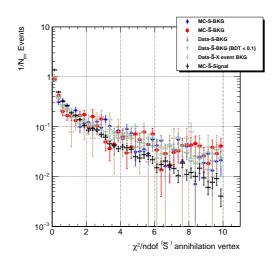

189 10 Sexaguarks 10.1 189 Introduction 10.2 Exotic hadrons 189 10.3 The H-dibaryon 190 10.4 191 10.5 192 193 10.6 194 10.6.2 Search channels at hadron colliders ..... 194 10.7 Adopted search strategy 195 10.8 196 198 10.9 10.10 Signal simulation 200 200 202 202 10.10.4 Influence of neutron Fermi momentum 204 209 211 10.11 Signal reconstruction efficiency 215 221 10.13 Systematic uncertainties 226 226 10.13.2 Number of pp collisions 234

187

viii

|     | 10.13.3 S as background reference10.14 Limit setting and results10.14.1 Limit setting introduction10.14.2 Results10.15 Summary and outlook10.16 Author's contribution | 234<br>235<br>235<br>236<br>240<br>242 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| A   | MPA and SSA SEU cross sectionsA.1SSA high latencyA.2SSA low latencyA.3MPA high latencyA.4MPA low latency                                                              | <b>245</b><br>245<br>246<br>247<br>248 |

| В   | Full CIC start-up sequence                                                                                                                                            | 249                                    |

| C   | CBC configurations for CBC-CIC start-up                                                                                                                               | 251                                    |

| D   | <b>Š</b> events: reconstruction efficiencies                                                                                                                          | 253                                    |

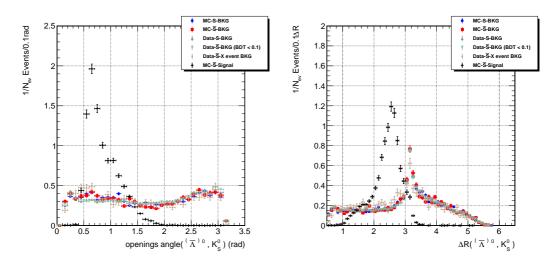

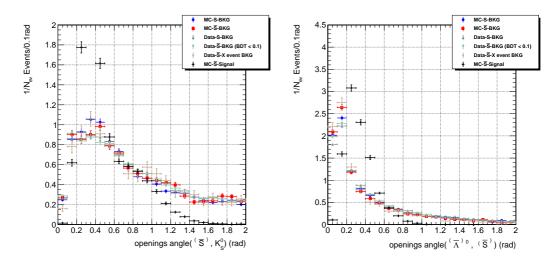

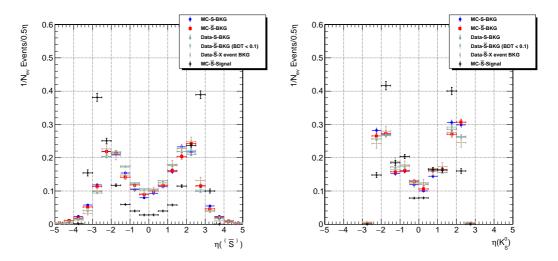

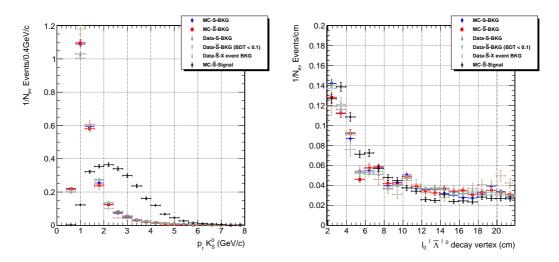

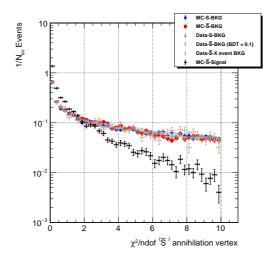

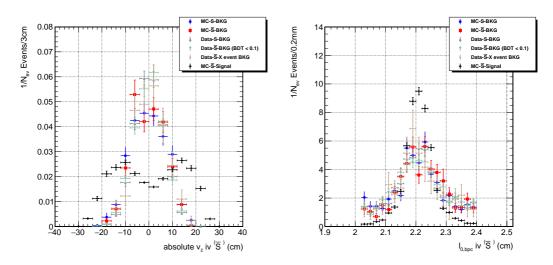

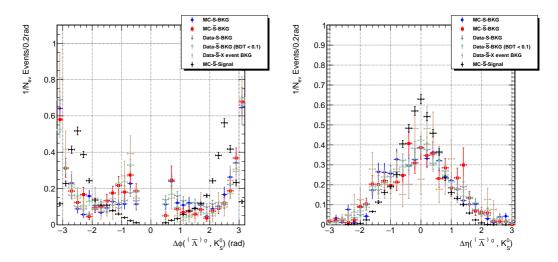

| Ε   | Input variables to the Sexaquark BDT: pre-BDT                                                                                                                         | 259                                    |

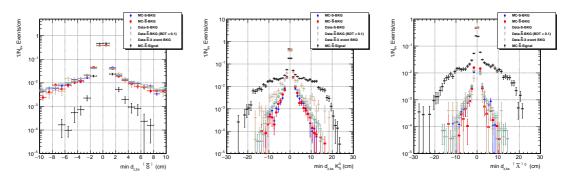

| F   | Input variables to the Sexaquark BDT: post-BDT                                                                                                                        | 265                                    |

| Lis | st of Abbreviations                                                                                                                                                   | 271                                    |

| Ac  | knowledgements                                                                                                                                                        | 275                                    |

| Bil | bliography                                                                                                                                                            | 277                                    |

# Summary

The Standard Model of particle physics describes the interactions between particles at the smallest known scale. The Standard Model has passed many tests with flying colours, but several observations, such as the need for dark matter, do not find an explanation in this framework. The Large Hadron Collider (LHC) at CERN is an excellent tool to study the Standard Model and to try and find answers to the open questions. The LHC collides protons resulting in a center of mass energy of 13 TeV, the highest energies ever attained at a particle collider. This enables physicists to study matter at an energy scale which is normally not accessible and which reflects the energy density in our Universe a fraction of a second after the Big Bang.

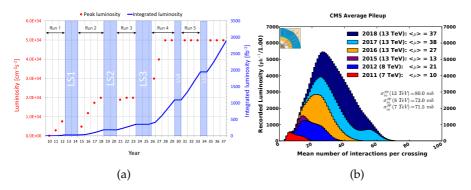

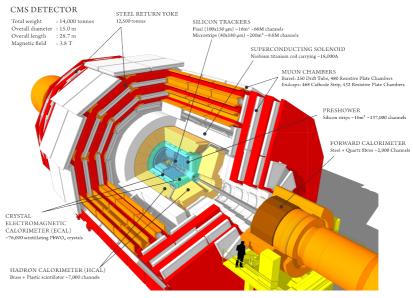

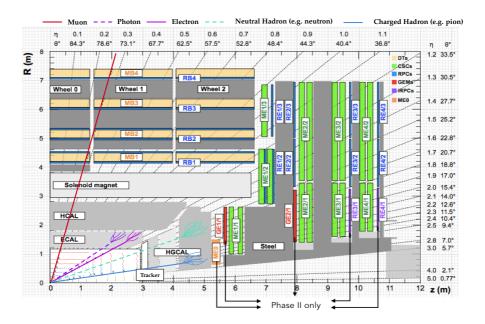

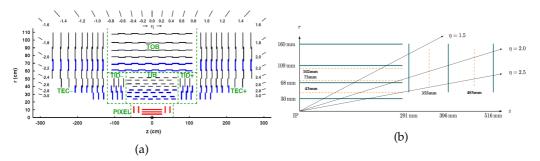

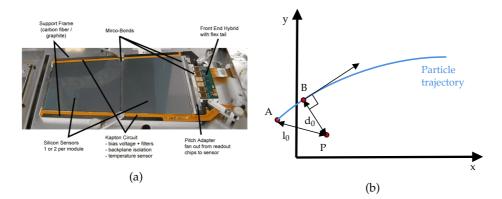

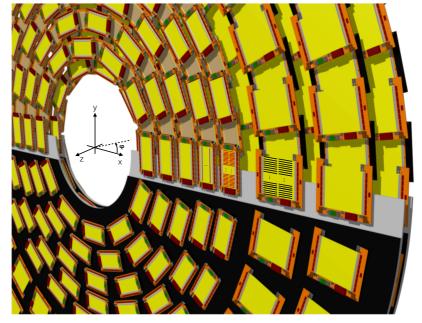

At one of the four interaction points along the LHC, the Compact Muon Solenoid (CMS) experiment is located. This general purpose experiment is designed to give an as good as possible measurement of the kinematic properties of the particles produced in a collision. CMS does this by using several subdetectors, one of which is the tracking system. The CMS tracker is based on silicon technology and consists of a pixel and a strip detector, designed to reconstruct the tracks of charged particles. The strip detector has been taking data since the start of the operation of the LHC in 2010 and will continue to do so until 2024. During the 2025-2027 Long Shutdown of the LHC, the accelerator complex will be upgraded to start the High Luminosity LHC (HL-LHC) phase at the end of 2027, which will provide the experiments with higher luminosities by increasing the number of proton-proton collisions per bunch crossing (pileup). In order to keep tracking performance at pre-HL-LHC levels in this harsher HL-LHC environment, the strip tracker will be replaced by an Outer Tracker, consisting of pixel-strip (PS) and strip-strip (2S) modules. These modules have local track reconstruction logic. The output of this logic is used as input to the L1 trigger system.

This thesis consists of a hardware part, focussing on the testing of Outer Tracker prototypes, and a search for new physics using the data collected by the CMS experiment.

#### The Upgraded Outer Tracker for the CMS Detector at the High Luminosity LHC:

Over the past years, Outer Tracker prototype ASICs and modules have become available. These require a dedicated test bench for characterization. This thesis discusses in detail the Phase-2 Outer Tracker and the structure and scope of the firmware project ( $\mu$ DTC) set up to read out ASIC and module prototypes of this new detector. The test bench is designed to test both 2S and PS modules and components. Several tests, to which the author contributed, are presented, going from bench-top testing of single ASICs, through radiation hardness testing of these chips and operating module prototypes in test beams.

#### Search for Composite Standard Model Dark Matter with CMS at the LHC:

The Sexaquark (S), composed of uuddss quarks, is a hypothetical particle that was proposed to be stable and a potential dark matter candidate.  $\bar{S}$  particles could be produced in the proton-proton collision and could subsequently annihilate on a neutron in the beampipe or detector material. This annihilation could result in a K<sup>0</sup><sub>S</sub> and  $\bar{\Lambda}^0$  which in turn can decay to charged products which are reconstructable with the CMS

tracker. This is the signal used in this thesis to look for the  $\bar{S}$  in the CMS 2016 dataset by reconstructing the  $\bar{S}$  kinematic properties and its annihilation vertex. The difficulties of reconstructing such a low momentum, displaced and off-pointing signature with the default CMS reconstruction algorithms will be studied and a first-ever limit on the  $[\sigma(p+p\to\bar{S})\times\sigma(\bar{S}+n\to K^0_S+\bar{\Lambda}^0)]$  cross section will be presented.

# Samenvatting

Het Standaardmodel van de deeltjesfysica beschrijft de interactie tussen deeltjes op de kleinste schaal. Dit model heeft reeds vele testen doorstaan. Toch vinden verschillende observaties - zoals de nood aan donkere materie - geen verklaring in dit framework. De Large Hadron Collider (LHC) aan het CERN is een excellent platform om het Standaardmodel te bestuderen en om antwoorden te vinden op onbeantwoorde vragen. De LHC versnelt protonen om ze nadien te laten botsen bij een massamiddelpuntsenergie van 13 TeV. Dit is de hoogste energie ooit bereikt in een laboratorium en daardoor stelt de LHC fysici in staat om materie te bestuderen bij een energieschaal die normaal niet toegankelijk is en die de energiedichtheid van ons universum reflecteert een fractie van een seconde na de Big Bang.

Aan één van de vier interactiepunten van de LHC bevindt zich het Compact Muon Solenoid (CMS) experiment. Dit experiment is ontworpen om een zo goed mogelijke meting te maken van de kinematische eigenschappen van de deeltjes die geproduceerd worden bij een botsing. CMS doet dit door gebruik te maken van verschillende subdetectoren. Een van deze subdetectoren is de sporendetector. De CMS-sporendetector is gebaseerd op siliciumtechnologie en bestaat uit een pixel- en een stripdetector. Deze detectoren zijn ontworpen om het pad van geladen deeltjes te reconstrueren. De huidige stripdetector is in gebruik sinds het begin van de LHC-exploitatie in 2010 en zal verder operationeel zijn tot 2024. Tijdens de Long Shutdown in 2025-2027 zal het versnellercomplex geüpgraded worden om de hogeluminositeitsfase (HL-LHC) van de LHC aan te vatten eind 2027. De HL-LHC zal de experimenten voorzien van hogere luminositeit door het aantal proton-proton botsingen per bundelkruising te verhogen. Om de performantie van de sporenreconstructie te garanderen in deze moeilijke omstandigheden zal de stripdetector vervangen worden door een nieuwe Outer Tracker. Deze subdetector zal bestaan uit twee soorten detectormodules: pixel-strip (PS) en strip-strip (2S) modules. Deze modules hebben logica om lokaal sporen te reconstrueren. De output van deze logica wordt gebruikt als input voor het L1-trigger-systeem.

Deze thesis bestaat uit een hardware-gedeelte, dat focust op het testen van Outer Tracker-prototypes, en een zoektocht naar nieuwe fysica, gebruikmakend van data verzameld door het CMS-experiment:

# *De Upgrade van de Buitenste Sporendetector van de CMS-detector voor de Hoge Luminositeit LHC:*

De prototype ASICs en modules voor de Outer Tracker vereisen een specifieke testopstelling voor karakterisatie. Deze thesis beschrijft in detail de Outer Tracker en het doel en de structuur van het firmware-project ( $\mu$ DTC) dat werd opgezet om prototypes van ASICs en modules van deze nieuwe detector uit te lezen. De testopstelling is ontworpen om zowel 2S als PS modules en componenten te testen. Verschillende testen, waaraan de auteur heeft bijgedragen, worden voorgesteld: testen van standalone chips, testen van chips onder straling en de kwalificatie van prototype modules in test beams.

#### Zoektocht naar Samengestelde Standaardmodel Donkere Materie met CMS aan de LHC:

Het Sexaquark-deeltje (S), met uuddss quark-inhoud, is een hypothetisch deeltje dat stabiel kan zijn. Mits de juiste eigenschappen is het deeltje ook een donkeremateriekandidaat.  $\bar{S}$  deeltjes kunnen geproduceerd worden bij proton-proton botsingen en kunnen nadien annihileren op neutronen in de bundelpijp of detectormateriaal. Deze annihilatiereactie kan aanleiding geven tot de vorming van een  $K_S^0$  en een  $\bar{\Lambda}^0$  die kunnen vervallen naar geladen dochterdeeltjes. Deze geladen deeltjes kunnen gereconstrueerd worden met behulp van de CMS-sporendetector. Dit is het signaal dat gebruikt wordt in deze thesis om te zoeken naar  $\bar{S}$  in de CMS 2016 dataset door de kinematische eigenschappen en de annihilatievertex van de  $\bar{S}$  te reconstrueren. De moeilijkheid van het reconstrueren van een dergelijk signaal met de standaard CMS-reconstructiealgoritmes wordt onderzocht en een limiet op  $[\sigma(p + p \rightarrow \bar{S}) \times \sigma(\bar{S} + n \rightarrow K_S^0 + \bar{\Lambda}^0)]$  wordt afgeleid.

# **Author's Contribution**

The author contributed to the development and use of the test system for CMS Phase-2 Outer Tracker ASICs and module prototypes and was the main developer of a first search for Sexaquarks at the CMS experiment. The contributions of the author are specified at the end of the chapters where the work is described and are summarised briefly below.

The work on the test system consisted of development, testing and maintenance of firmware blocks. The author then contributed to the testing of single chips, ASIC irradiation tests, integration tests and test beams with prototype modules and analysed the results of these tests. This work resulted in the following, two of which are still to be published, papers:

- CMS Tracker Collaboration, "Test beam demonstration of silicon microstrip modules with transverse momentum discrimination for the future CMS tracking detector", JINST 13 (2018) no.03, P03003, (2018-03-06), DOI: 10.1088/1748-0221/13/03/P03003

- CMS Tracker Collaboration, "Beam Test Performance of Prototype Silicon Detectors for the Outer Tracker for the Phase-2 Upgrade of CMS", CERN-CMS-NOTE-2019-006, *submitted to JINST*

- CMS Tracker Collaboration, "Performance of the Prototype CBC3-based Outer Tracker Modules for the Phase II Upgrade of CMS before and after neutron irradiation", *in preparation*

and following proceedings:

- T. Gadek et al., "Quality Control Considerations for the Development of the Front End Hybrid Circuits for the CMS Outer Tracker Upgrade", TWEPP2017, POS proceeding, Volume 313, DOI: https://doi.org/10.22323/1.313.0061

- D. Ceresa et al., "Characterization of the MPA prototype, a 65 nm pixel readout ASIC with on-chip quick transverse momentum discrimination capabilities", TWEPP 2018, POS proceeding, Volume 343, DOI: https://doi.org/10.22323/1.343.0166

- A. Caratelli et al., "Characterization of the first prototype of the Silicon-Strip readout ASIC (SSA) for the CMS Outer-Tracker phase-2 upgrade", TWEPP2018, POS proceeding, Volume 343, DOI: https://doi.org/10.22323/1.343.0159

- A. Caratelli et al., "Low-power SEE hardening techniques and error rate evaluation in 65nm readout ASICs", TWEPP2019, POS proceeding, *submitted*

- B. Nodari et al., "First results of CIC data aggregation ASIC for the future CMS tracker", TWEPP2019, POS proceeding, *submitted*

- M. Kovacs et al., "A High Throughput Production Scale Front-End Hybrid Test System for the CMS Phase-2 Tracker Upgrade", TWEPP2019, POS proceeding, *submitted*

J. De Clercq et al., "OT-µDTC, a test bench for testing CMS Outer Tracker Phase-2 module prototypes", EPS-HEP2019, POS proceeding, *submitted*

The work on this test system was recognized by the CMS collaboration by awarding a 2018 CMS detector award to the author for "Significant contributions to the baseline DAQ for the Phase-2 Outer Tracker, and for  $\mu$ DTC firmware design and implementation".

The author was the main developer for the Sexaquark search. Extracting a limit on  $[\sigma(pp \rightarrow \bar{S}) \times \sigma(\bar{S} + n \rightarrow K_S^0 + \bar{\Lambda}^0)]$  required setting up the signal reconstruction algorithm using dedicated vertexing and kinematic fitting techniques, implementing the simulation chain for this unique signal in the CMS simulation framework, including a non-standard encoding of its interaction using the GEANT toolkit, evaluating systematic uncertainties, investigating the background and using multivariate discrimination techniques to suppress it. Throughout this, several obstacles were tackled in searching for the Sexaquark signal with the CMS detector. The observations from these in-depth studies are key to guide the next Sexaquark search towards a more competitive result.

"In a distant and second-hand set of dimensions, in an astral plane that was never meant to fly, the curling star-mists waver and part... See... Great A'Tuin the turtle comes, swimming slowly through the interstellar gulf, hydrogen frost on his ponderous limbs, his huge and ancient shell pocked with meteor craters. Through sea-sized eyes that are crusted with rheum and asteroid dust He stares fixedly at the Destination. In a brain bigger than a city, with geological slowness, He thinks only of the Weight. Most of the weight is of course accounted for by Berilia, Tubul, Great T'Phon and Jerakeen, the four giant elephants upon whose broad and startanned shoulders the disc of the World rests, garlanded by the long waterfall at its vast circumference and domed by the baby-blue vault of Heaven. Astropsychology has been, as yet, unable to establish what they think about. The Great Turtle was a mere hypothesis until the day the small and secretive kingdom of Krull, whose rim-most mountains project out over the Rimfall, built a gantry and pulley arrangement at the tip of the most precipitous crag and lowered several observers over the Edge in a quartzwindowed brass vessel to peer through the mist veils. The early astrozoologists, hauled back from their long dangle by enormous teams of slaves, were able to bring back much information about the shape and nature of A'Tuin and the elephants but this did not resolve fundamental questions about the nature and purpose of the universe. For example, what was Atuin's actual sex? This vital question, said the Astrozoologists with mounting authority, would not be answered until a larger and more powerful gantry was constructed for a deep-space vessel. In the meantime they could only speculate about the revealed cosmos. There was, for example, the theory that A'Tuin had come from nowhere and would continue at a uniform crawl, or steady gait, into nowhere, for all time. This theory was popular among academics. An alternative, favoured by those of a religious persuasion, was that A'Tuin was crawling from the Birthplace to the Time of Mating, as were all the stars in the sky which were, obviously, also carried by giant turtles. When they arrived they would briefly and passionately mate, for the first and only time, and from that fiery union new turtles would be born to carry a new pattern of worlds. This was known as the Big Bang hypothesis."

> Terry Pratchett The Colour of Magic

# Part I Setting the Stage

# Chapter 1 Preamble

If you do not measure, you do not know and the Universe might as well be existing of giant tortoises...

The world as pictured in the quote at the start of this thesis from Terry Pratchet's novel "The Colour of Magic" is perhaps not physically exactly correct (at least not for our Universe), but it does exemplify the need for fundamental research, which would otherwise make the professions of astrozoologist and astropsychologist not completely redundant.

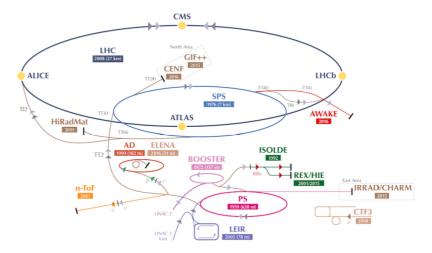

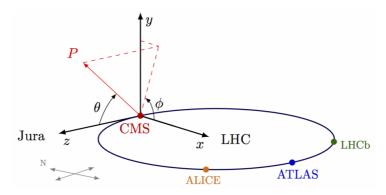

The Large Hadron Collider (LHC) at CERN (European Organization for Nuclear Research) together with the CMS (Compact Muon Solenoid) experiment allow physicists to study, in a laboratory environment, the laws of physics at a new energy frontier. At the LHC two beams of protons are accelerated in opposite direction and are made to collide at four interaction points along the accelerator ring. At one of these interaction points the CMS experiment is located. By detecting the particles which are created during a collision, already known processes can be studied in more detail or signatures of undiscovered particles might be found. The discovery potential of the LHC was already proven by experimentally confirming the existence of the Higgs boson.

The Higgs particle and its properties fit within current accuracy in the Standard Model of particle physics. Astronomical and cosmological observations, as well as theoretical considerations, hint however at physics beyond the Standard Model. The data taken by the CMS experiment already allowed for putting tight limits on several beyond the Standard Model models, but other searches as well as high precision Standard Model measurements could benefit from a larger dataset. Therefore, the LHC will run at a higher luminosity from 2026 onwards<sup>1</sup>. This requires the experiments, such as CMS, to upgrade their detectors. One of the foreseen upgrades is a full replacement of the CMS Tracker.

Performing better Standard Model measurements or experimentally investigating physics beyond the Standard Model requires a long process to be followed. From a bird's eye view this process consists of following steps: theoretical predictions, experiment design often including detector R&D and prototyping, experiment construction, detector operation, data analysis and hopefully at the end discovery. This thesis essentially splits up into and touches upon two parts of the aforementioned process applied to the CMS experiment:

- Detector prototyping: data acquisition development for, and testing of, CMS Phase-2 Outer Tracker prototype ASICs and module prototypes.

- Data analysis: search for the Sexaquark particle, a Standard Model composite dark matter candidate of which the anti-particle could initiate a signal in the CMS tracker.

<sup>&</sup>lt;sup>1</sup>This thesis, with the exception of the Summary, adopts the pre-December 2019 LHC schedule with Long Shutdown 3 planned from 2024 until 2026. According to the latest schedule of the LHC, the Long Shutdown 3 is planned from 2025 until 2027.

The above two parts are stand-alone research subjects with as commonality the CMS experiment and more specifically the CMS tracker subdetector. This thesis is therefore built up as follows: the first part is a general introduction to the thesis and contains useful introductory information for both research topics. It gives an introduction to particle physics, detector techniques for particle physics experiments and the CMS experiment. More details are provided on the outstanding problem of dark matter, silicon based detectors and on the CMS tracker subdetector as these topics are particularly relevant for the rest of the work. A good understanding of the full CMS detector is essential to understand the role of the tracker subdetector in the full experiment and the reason for the upgrade of this subdetector. This upgrade is the topic of the second part of the thesis which starts with an introduction on the CMS Phase-2 Outer Tracker upgrade and proceeds with the tests performed on several prototypes. The third, and last part of this thesis, introduces the Sexaquark particle and discusses the search for this particle using 2016 RunG and RunH data from the CMS experiment.

# **Chapter 2**

# **Introduction to Particle Physics**

## 2.1 Introduction

Elementary particle physics tries to explain the nature and interaction of matter at the smallest scales. Decades of experiments have contributed to the development of the *Standard Model of particle physics* which classifies the elementary particles and describes the fundamental forces which act between them. This chapter gives an overview of the Standard Model (section 2.2), an introduction to its theoretical basis (section 2.3) and a description of one of its shortcomings: explaining the nature of *dark matter* (section 2.4).

## 2.2 The Standard Model of particle physics

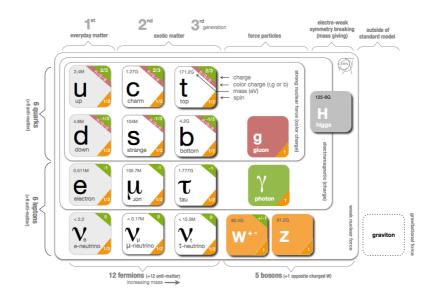

Figure 2.1 shows the building blocks of the Standard Model of particle physics. As far as we know, all known matter is built up of fermions which are particles with half-integer spin. The fermions are divided in leptons and quarks and both of these particle types are arranged into three generations which have increasing masses. Particles belonging to higher generations are heavier and unstable and when they are produced they eventually decay back to particles from the first generation. Each of the fermions has an anti-matter counterpart which has all the charges reversed.

The fermions interact through the exchange of particles with integer spin, the bosons. Each one of the bosons can be linked to a fundamental force. The most familiar boson is the photon ( $\gamma$ ) which mediates the electromagnetic force. The W<sup>±</sup> and Z bosons mediate the weak force and are apparent for example in nuclear decays. The gluon (*g*) is linked to the strong force, which e.g. binds quarks in nuclei and keeps protons and neutrons together in the atomic nucleus. The fourth fundamental force, gravity, has not yet been described in the Standard Model.

There are six different *flavours* of quarks in the Standard Model: up, down, charm, strange, top and bottom. Quarks have a *colour* charge and they cannot exist isolated, a property of the strong interaction called confinement, which only allows colour neutral states to propagate freely. A whole spectrum of bound states of quarks, so-called hadrons, has been discovered. Hadrons built up from an even number of *valence quarks*<sup>1</sup> (e.g.  $K_S^0$ ) are referred to as mesons whilst particles consisting of an odd number of valence quarks (e.g.  $\Lambda^0$ ) are referred to as baryons. Next to a colour charge, the quarks have a weak charge (*flavour*) and a fractional electric charge which makes them also interact through the electroweak interaction.

Leptons on the other hand are not subject to the strong interaction. Leptons come in pairs: each charged lepton is associated with a neutrino. Neutrinos are massless in the Standard Model. They also do not have an electric charge and therefore only interact

<sup>&</sup>lt;sup>1</sup>The quarks and anti-quarks which give rise to the quantum numbers of the hadron.

FIGURE 2.1: Elementary particles of the Standard Model [1].

through the weak interaction which makes them notoriously difficult to detect experimentally.

Fermions and massive bosons get their mass through interaction with the Brout-Englert-Higgs (BEH) field [2, 3], or in short Higgs field, of which the Higgs bosons are the excitations. The BEH mechanism will be discussed in more detail in section 2.3. The interaction between the fundamental particles is described using a Quantum Field Theory (QFT), which is the subject of the next section.

## 2.3 The mathematical framework of the Standard Model

The interactions between elementary particles happen at the smallest distance scales with energies typically higher or comparable to the particle's mass. Using a QFT approach, both quantum mechanics and relativity are included to describe the particle interactions. The solutions of the relativistic Schrödinger equations in the QFT are fields and the quantization of these fields are linked to particles in the Standard Model. An extensive discussion on QFT and the Standard Model can be found for example in Ref. [4].

The QFT description starts with a Lagrangian ( $\mathcal{L}$ ), describing the field, from which the equation of motion can be extracted by minimising the action ( $\mathcal{S}$ ) defined as:

$$S = \int \mathcal{L}(x) \, d^4x, \tag{2.1}$$

where *x* is the space-time coordinate. The Standard Model Lagrangian comprises specific terms for each of the fundamental interactions.

The Lagrangian of a free fermion contains a kinetic and a mass term:

$$\mathcal{L}_{Dirac} = i\bar{\psi}\gamma^{\mu}\partial_{\mu}\psi - m\bar{\psi}\psi, \qquad (2.2)$$

where the Einstein convention is adopted of summation over repeated indices, *m* is the fermion's mass,  $\gamma^{\mu}$  are the Dirac matrices ( $\gamma^{\mu}\gamma^{\nu} + \gamma^{\nu}\gamma^{\mu} = 2g^{\mu\nu}$  with  $g^{\mu\nu}$  the Minkowski metric) and  $\psi$  and  $\bar{\psi} (= \psi^{\dagger}\gamma^{0})$  represent the fermion and anti-fermion fields respectively. The modulus  $|\psi|^{2}$  as well as the Lagrangian are required<sup>2</sup> to be invariant under local phase transformations:

$$\psi \to \psi' = U(x)\psi = e^{i\vec{\alpha}(x) \cdot \frac{\tau}{2}}\psi, \qquad (2.3)$$

with  $\vec{\tau}$  the generators of a Lie group and  $\vec{\alpha}(x)$  rotation parameters. To get the first term in the Lagrangian in Equation (2.2) invariant under this gauge symmetry, the derivative can be replaced by its covariant form:

$$D_{\mu} = \partial_{\mu} + ig\frac{\vec{\tau}}{2} \cdot \vec{A}_{\mu}, \qquad (2.4)$$

where  $\vec{A}_{\mu}$  is a vector field which couples to the fermions with a coupling strength *g* and which transforms according to  $A_{\mu} \rightarrow A'_{\mu} = A_{\mu} - \partial_{\mu}\alpha$ . Combining Equation (2.2) and (2.4) gives a new Lagrangian:

$$\mathcal{L}_{Dirac} = i\bar{\psi}\gamma^{\mu}D_{\mu}\psi - m\bar{\psi}\psi, \qquad (2.5)$$

which is indeed invariant ( $\mathcal{L}_{\psi} = \mathcal{L}_{\psi'}$ ) under the local gauge symmetry (Equation (2.3)). The above principle naturally gives rise to a new field ( $\vec{A}_{\mu}$ ) which is the gauge field associated to the gauge transformation which was performed. This field allows information to be propagated from one matter field to another.

The same principle can be applied using other symmetry groups than the one used in Equation (2.3) and can be extended to the full Standard Model Lagrangian which is invariant under the symmetry group<sup>3</sup>  $G_{SM}$ :

$$G_{SM} = SU(3) \times SU(2) \times U(1). \tag{2.6}$$

SU(3) represents the symmetry of the theory describing the strong force, quantum chromodynamics (QCD) with coupling strength  $g_s$ , whilst  $SU(2) \times U(1)$  describes the symmetry of the electroweak theory which combines the weak and the electromagnetic interaction. The covariant derivative leaving the full Standard Model Lagrangian invariant under the transformation  $G_{SM}$  is:

$$D_{\mu} = \partial_{\mu} + ig_{s} \frac{\lambda_{a}}{2} G_{\mu}^{a} + ig \frac{\sigma_{i}}{2} W_{\mu}^{i} + ig' \frac{\gamma}{2} B_{\mu}, \qquad (2.7)$$

where the second term represents the strong force and its SU(3) symmetry, with the Gell-Man matrices  $\lambda_a$  (a = 1...8) as generators. It introduces eight gluon fields of which the massless gluons are excitations. The third and fourth term are associated to the electroweak interaction. The electroweak  $SU(2) \times U(1)$  symmetry group, with generators  $\sigma_i$  (i=1...3), the Pauli matrices, and Y the hypercharge, introduces 3 gauge fields  $W^{\alpha}_{\mu}$  and one gauge field  $B_{\mu}$ . The electroweak coupling strengths g and g' are linked through the weak

<sup>&</sup>lt;sup>2</sup>The argument for introducing this requirement is that if there is no way for fields to communicate through space and time, a local change in their phase should not change the physics of the problem.

$<sup>{}^{3}</sup>SU(n)$  are the groups of  $n \times n$  unitary matrices of determinant 1. The dimension of a group is given by  $n^{2}$  for U(n) groups and  $n^{2}$ -1 for SU(n).

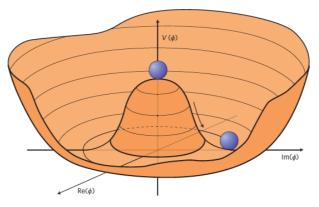

FIGURE 2.2: Mexican hat potential [5].

mixing angle

$$\tan \theta_W = \frac{g'}{g} \tag{2.8}$$

and the physically observed bosons  $W_{\mu}^{-}$ ,  $W_{\mu}^{+}$ ,  $Z_{\mu}$  and  $A_{\mu}$  (the photon) are formed by mixing the  $W_{\mu}^{i}$  fields, associated to the SU(2) symmetry, and the  $B_{\mu}$  field, associated to the U(1) symmetry:

$$W_{\mu}^{\pm} = \sqrt{\frac{1}{2}} \left( W_{\mu}^{1} \mp i W_{\mu}^{2} \right)$$

(2.9)

$$Z_{\mu} = W_{\mu}^3 \cos \theta_{\rm W} - B_{\mu} \sin \theta_{\rm W} \tag{2.10}$$

$$A_{\mu} = W_{\mu}^3 \sin \theta_W + B_{\mu} \cos \theta_W. \tag{2.11}$$

The above theory is however unable to assign a non-zero mass to the gauge bosons without breaking the gauge invariance. The mechanism introduced to explain the particle masses without breaking the gauge invariance of the Standard Model Lagrangian is the Brout-Englert-Higgs mechanism. This mechanism introduces a complex scalar doublet ( $\phi$ ) which has a non-zero vacuum expectation value v. The Higgs field Lagrangian is:

$$\mathcal{L}_{H} = \left(D^{\mu}\phi\right)^{\dagger} \left(D_{\mu}\phi\right) - V(\phi), \qquad (2.12)$$

with the potential  $V(\phi)$ :

$$V(\phi) = \mu^2 \phi^{\dagger} \phi - \lambda \left(\phi^{\dagger} \phi\right)^2, \qquad (2.13)$$

where  $\lambda$  represents the self coupling strength and  $\mu$  is a mass parameter. If  $\mu^2 < 0$  and  $\lambda < 0$  this potential is known as the *Mexican-hat potential* which is depicted in Figure 2.2.

The BEH mechanism allows for the three observable massive weak gauge bosons to acquire a mass whilst the photon can remain massless. The excitations of the scalar field  $\phi$  introduced here are the Higgs bosons. Fermions acquire mass by the addition of *Yukawa* terms, of the form  $g_y \bar{\psi} \phi \psi$ , to the Standard Model Lagrangian where  $g_y$  represents the coupling strength of the scalar field to the fermion.

The Standard Model as introduced in the previous section and its mathematical basis depicted in this section describe high energy physics experiments to high accuracy.

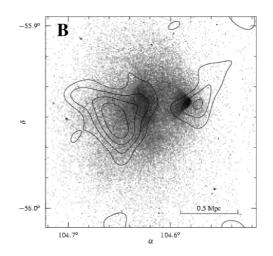

FIGURE 2.3: Image of 1E0657-558 [7]. The black contours are the mass contours extracted from weak lensing. Each contour represents a change in the surface mass density of  $2.8 \times 10^8 \, M_\odot / kpc^2$ . The grey-scale is the X-ray image of the hot gas obtained from the Chandra Observatory. The so-called bullet cluster is visible on the right in the grey-scale.

Experimental observations however suggest that extensions of the Standard Model are needed as the Standard Model for example does not explain the difference in the electroweak and gravitational scale (*hierarchy problem*), the neutrino masses, the matter-antimatter asymmetry in the Universe nor does it predict the existence of dark matter. The latter will be discussed in more detail in the next section as the dark matter problem is relevant for the search described in Chapter 10.

## 2.4 Dark matter

#### 2.4.1 Introduction

The nature of dark matter, together with e.g. baryon asymmetry, the hierarchy problem and the neutrino masses is one of the main mysteries in particle physics. All of these do not find a place in the Standard Model. Dark matter does not appear to interact via the electromagnetic force and thus would not absorb, reflect or emit any light, hence its name. Until today, only gravitational evidence for the existence of dark matter is available and this through astronomical and cosmological observations. Measurements show that our Universe is built up of roughly 5% known matter,  $\approx 27\%$  dark matter and  $\approx 68\%$  dark energy [6].

#### 2.4.2 Evidence for dark matter

A particularly instructive example of evidence for the existence of dark matter is 1E 0657-558 [7], also known as *the bullet cluster*, which is shown in Figure 2.3. In this figure the grey-scale shows the mass distribution derived from X-ray measurements of hot gas, which represents the majority of the baryonic matter in the cluster. It reveals the shape of a large galaxy cluster on the left and a smaller cluster which demonstrates a shock-wave on the right. The right cluster obtained this specific shape (a bullet) by passing through the large cluster. Using the effect of gravitational lensing, the total mass distribution of both clusters can be extracted. The obtained mass distributions are shown as the contours in Figure 2.3. Comparing the distribution of the hot gas with the total mass distribution shows a clear offset. This is a smoking gun for the existence of dark matter: the gas in the clusters is slowed down due to frictional electromagnetic forces. The dark matter on the other hand is not affected by this friction and travels further on its path, in this way splitting off from the gas. Similar observations were done in other colliding galaxy clusters such as MACS J0025.4-1222 [8].

These colliding clusters are historically not the first evidence for dark matter. It was F. Zwicky whom in 1933 measured the velocity of galaxies in clusters and found that the visible mass in the clusters could not deliver the gravitational pull to keep the galaxies on their orbit [9]. He therefore conjectured that additional matter needs to be present in the cluster to deliver the extra mass. This type of matter he called *dark matter*. Similar observations can be done on a smaller scale by looking at stars within a galaxy.

Besides colliding galaxy clusters and galaxy rotation curves, evidence for dark matter was also found in the Cosmic Microwave Background (CMB) [10, 11]. The CMB is a remnant from the photon decoupling which happened when the Universe was about 379,000 years old. The decoupling took place when the energy density after the Big Bang dropped below the energy threshold for the photons to ionize hydrogen and maintain a hydrogen plasma. Hydrogen atoms could now stay combined and photons could move freely. These photons can still be observed today, although as less energetic ones due to the expansion of the Universe. This relic radiation, having a thermal black body spectrum, can be observed using radio telescopes. Small perturbations in the CMB, measured over the full sky, reflect, amongst others, information on the small anisotropies in matter density at the time of decoupling.

One of the most important results of the study of the CMB are the measurements of the mass density of several types of matter in our Universe. The Planck collaboration for example quotes [6] a dark matter density and baryon density of respectively  $\Omega_c h^2 = 0.120 \pm 0.001$  and  $\Omega_b h^2 = 0.0224 \pm 0.0001$ . Here  $\Omega_X = \rho_X / \rho_{crit}$  for a component X with  $\rho_{crit}$  the critical mass density which means that the total mass density  $\Omega_{tot} = 1$  corresponds to a flat Universe and *h* is the Hubble constant in units of 100 km/(s.Mpc).

The observation of old galaxies at a redshift of  $\approx 10$  together with the small density perturbations seen in the CMB also require extra matter, besides the visible component, in order for these old galaxies to could have formed [10]. Without dark matter the density perturbations would not start to grow into galaxies at such an early stage. Furthermore this dark matter should be *cold* which means that it should have been non-relativistic at the start of galaxy formation. This implies for example that neutrinos cannot be the dark matter: neutrinos were kept in equilibrium with photons and electrons through  $\gamma \leftrightarrow e^+ + e^- \leftrightarrow v_i + \bar{v}_i$ . This reaction stopped at around 3 MeV, leaving behind a relic relativistic population of neutrinos. An upper bound on the contribution of light neutrinos to the dark matter can be extracted from analysis of structure formation:  $\Omega_{\nu}h^2 \leq 0.0062$ (at 95% CL) [10].

#### 2.4.3 Dark matter candidates

Many candidates for dark matter have already been proposed. Some of them are hard to detect Standard Model particles, but most are completely new exotic particles. The constraints on dark matter candidates are numerous. M. Taoso, G. Bertone and A. Masiero summarise in Ref. [12] a 10-point test for a dark matter candidate:

- 1. Does it match the appropriate relic density? Non-relativistic dark matter, first being in thermodynamic equilibrium with the plasma in the early Universe freezes-out when its interaction rate drops below the expansion rate of the Universe. The remaining relic density today can be calculated for a given dark matter candidate and should be within the bounds of the limits set by CMB measurements.

- 2. Is it cold? This constraint was already explained in the previous section. Only a small part of the dark matter content of the Universe is allowed to be hot dark matter in order not to jeopardize the early onset of galaxy formation.

- 3. Is it neutral? Most dark matter candidates have to be neutral to explain the fact that they do not interact through the electromagnetic interaction. Only in specific models the dark matter candidate is allowed to have an electric charge. These models will not be discussed here.

- 4. Is it consistent with Big Bang nucleosynthesis? A set of Boltzmann equations can explain the measured abundances of light nuclei in the context of Big Bang nucleosynthesis (BBN) to very high accuracy. A dark matter candidate should therefore not introduce stress on the BBN model which is described very well by Standard Model processes. E.g. introducing dark matter which in decays would generate photons which in turn could alter the formation process of light nuclei would be a direct constraint on this type of dark matter.

- 5. Does it leave stellar evolution unchanged? Dark matter candidates can be produced in the center of stars and if the candidates only interact weakly they can furthermore leave the star. This would represent an energy loss channel which could possibly alter the evolution of the star. Several measurements, for example the measurement of the neutrino flux, neutrino energy and the duration of supernova SN1987A put limits on these additional channels.

- 6. Is it compatible with constraints on self-interactions? Multiple observations put constraints on the self-interaction cross section of dark matter particles. One example of these measurements are the colliding clusters described in the previous section from which an upper limit on the dark matter self-interaction can be extracted. Another observation is the *core-cusp* problem, which is the discrepancy seen in material distribution between the cuspy dark matter haloes predicted in cold dark matter N-body simulations and the actual observed distribution in e.g. dwarf galaxies. Self-interacting dark matter could alleviate this problem by smoothing the cuspy profile. Recent measurements [13] show however that the core-cusp problem can also be resolved by taking into account the effect of bursty star formation which can kinematically heat up dark matter at the center of galaxies through fluctuations in the gravitational potential.

- 7. Is it consistent with direct DM searches? As will be discussed in section 2.4.4, direct detection of dark matter through detection of nuclear recoils has put several constraints on the dark matter interaction cross section versus mass of the dark matter particle.

- 8. Is it compatible with gamma-ray constraints? As will be discussed in section 2.4.4, another way to look for dark matter candidates is by detection of their annihilation products. A good candidate product to look for are high energy photons. For mass ranges of the dark matter candidate in the GeV-TeV region this results in  $\gamma$ -rays. Non-observation of clear evidence of dark matter annihilation can put several constraints on dark matter candidates.

- 9. Is it compatible with other astrophysical bounds? Besides photons, also neutrinos can be formed directly or indirectly in annihilation of the dark matter particles. These neutrinos can subsequently be detected in high-energy neutrino telescopes through the detection of Cherenkov light from secondary muons produced when the neutrino interacts with the material. Other messengers such as positrons, antiprotons or X-rays could also give more information and put further limits on dark matter models.

- 10. Can it be probed experimentally? This is not a fundamental requirement for a good dark matter candidate, but it is a requirement to affirm the hypothesis.

A few candidates for dark matter were already mentioned above. Two other interesting examples of possible candidates are:

- Massive astrophysical compact halo objects (MACHOs): these are a natural solution to the dark matter problem as they do not require introducing any exotic particle. MACHOs are astronomical bodies composed of normal baryonic matter with typical masses of 0.001–0.1 solar masses. These objects emit only little or no radiation at all. Examples of MACHOs are (primordial) black holes and neutron stars. Major sky surveys have been set up to discover these objects through microlensing<sup>4</sup> without positive result [11].

- Weakly interacting massive particles (WIMPs): WIMPs are particles with masses roughly between 10 GeV/ $c^2$  and a few TeV/ $c^2$  and with cross sections comparable to the weak interaction. WIMPs freeze out once the rate of reactions which change WIMPs to Standard Model particles and vice versa becomes smaller than the Hubble expansion rate of the Universe. It is rather remarkable that when WIMPs are requested to explain the energy density of dark matter one naturally arrives at an interaction cross section which is in the order of magnitude range of the weak interaction. WIMPs therefore form a preferred solution to the dark matter problem. An example of a WIMP is the lightest superparticle in supersymmetric models with R-parity conservation [11].

It is of course not required that dark matter consists out of a single type of particle. Therefore e.g. combinations of the different possibilities listed above are also possible.

<sup>&</sup>lt;sup>4</sup>If the object acting as a lens has a small mass (compared to normal lensing where galaxies or clusters are the lensing object) it is not possible to distinguish multiple images of the lensed object. An amplification of the light can however be measured. MACHO events can be distinguished from variable stars using the fact that the amplification is the same for red and blue light.

Furthermore it is possible that dark matter is actually not required to explain the observations discussed in section 2.4.2. These observations rely on our current understanding of physics which might not be applicable at cosmological scales. Alternative theories can be postulated which rely on modifications to the laws of gravity to explain for example the rotation curves of stars in galaxies. Indeed, there is a valid basis for such theories as the acceleration of stars in the outer radius of galaxies is extremely small. This is a regime in which Newtonian dynamics has never been tested. It proves difficult however to reconcile all observations, in particular the CMB measurements, in such theories.

#### 2.4.4 Experimental searches for the nature of dark matter

Besides specific experiments designed to detect a certain type of dark matter, such as experiments looking for MACHOs, most dark matter experiments can be categorised into one of the following three types:

- Direct detection: the dark matter particles present in our galaxy are expected to interact with Standard Model particles through e.g. nuclear recoil interactions. The recoil nuclei can be recorded for example by detecting emitted scintillation light, induced charge or phonons.

- Indirect detection: dark matter particles can annihilate on their anti-matter partner and can result in e.g. γ-rays or neutrinos which can be detected with dedicated experiments. Regions with high mass density, such as the galactic center or the center of the Earth and the Sun are particularly interesting to study. Detection of γ-rays is most conveniently done in space based observatories because γ-rays do not penetrate the atmosphere (e<sup>+</sup>e<sup>-</sup> pair production) to reach ground based telescopes. Indirect detection of γ-rays is however possible using ground based telescopes which are sensitive to the Cherenkov light and secondary particles in a cosmic shower initiated by a γ-ray. As discussed in the previous section, also neutrinos, positrons, anti-protons, anti-nuclei, X-rays and measurements of radio emission can be used to either do independent searches or to complement measurements in any other channel.

- Production at particle colliders: dark matter particles can also be produced at collider experiments through the collision of two Standard Model particles. The produced dark matter particle could pass through the detector without leaving a signal, but it can be produced in association with other Standard Model particles. In a hermetic detector, the presence of the dark matter particle can then be inferred from the momentum imbalance in the total transverse<sup>5</sup> momentum.

## 2.5 Summary

The Standard Model of particle physics and its mathematical foundations which can be found in Quantum Field Theory describe particle physics phenomena to high accuracy. The known matter around us is built up of fermions which interact through the exchange of bosons. The mass of the bosons and fermions can be explained by interaction with the Higgs field. Astronomical, cosmological and theoretical considerations point at the existence of physics beyond the Standard Model. One of the outstanding problems is the

<sup>&</sup>lt;sup>5</sup>This is the plane transverse to the beam direction.

nature of dark matter. The evidence for dark matter is eclectic: colliding galaxies, rotation curves of stars in galaxies, CMB measurements,... The fact that dark matter is needed to explain these observations also implies that a dark matter model is constrained from many angles. Particle accelerators, such as the LHC, are a good platform to test several of these theories through the potential production of dark matter particles in high energy collisions.

# **Chapter 3**

# **Detector Techniques in Particle Physics**

## 3.1 Introduction

A good understanding of particle interactions with matter is required to both understand particle detection techniques and the radiation damage which these interactions can induce on detector components. An overview of particle interactions with matter is therefore given in section 3.2. The actual detection of charged particles will then be discussed in section 3.3 and the usage of silicon sensors for charged particle tracking detectors is described in section 3.4, which includes a brief summary on the effects of radiation on silicon sensors. An introduction to the basics on integrated circuits is provided in section 3.5 and more detail is given on readout ASICs (Application-Specific Integrated Circuits) for silicon tracking detectors in section 3.6. The effects of radiation on ICs (Integrated Circuits) is discussed in section 3.7.

## 3.2 Particle interactions with matter

Particles can interact in many different ways with matter. These interactions form the basis of particle detection. The particle interaction with matter depends on the type of particle which interacts. For the following discussion four particle categories are identified:

- Heavy charged particles

- Electrons

- Photons

- Heavy neutral particles

where the adjective *heavy* is used to distinguish other charged particles and neutral particles from electrons and photons respectively. The following sections will give a brief overview [14] of all four categories, going a bit more into depth on heavy charged particles as these are of importance for the rest of the work.

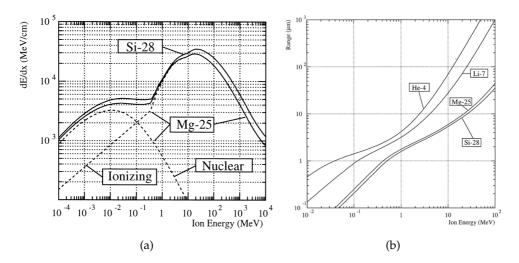

#### 3.2.1 Heavy charged particle interactions with matter

Heavy charged particles interact through the Coulomb force with the orbital electrons from the material. As a result of these interactions they excite orbital electrons or electronion pairs are formed. In several particle detectors the latter forms the basis for the detector response. In interactions where a lot of energy is transferred to the orbital electron, the orbital electron can gain enough energy to also create secondary ionization. In those cases the electrons are referred to as  $\delta$ -rays. Interactions of the incoming particle with

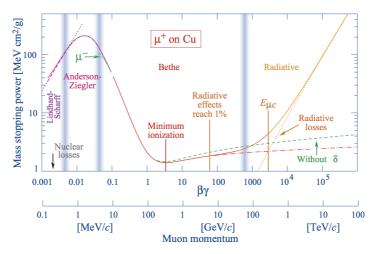

FIGURE 3.1: LET divided by the material density for positive muons in copper as a function of the muon momentum and  $\beta \gamma$  (=p/(Mc)). In the central region, the Bethe-Bloch approximation is valid. For lower ( $\beta \gamma \leq 0.1$ ) and higher (1000  $\leq \beta \gamma$ ) momenta other effects need to be taken into account [10].

the nuclei, such as Rutherford scattering, are also possible but are less probable than ionization interactions and are normally not exploited in radiation detectors.

The Linear Energy Transfer (LET):

$$LET = -\frac{dE}{dx} \tag{3.1}$$

describes the energy loss (dE) over a path length (dx). The LET for a muon is depicted in Figure 3.1 for nine orders of magnitude of the muon's energy.

The average LET for particles with  $0.1 \leq \beta \gamma \leq 1000$  (with  $\beta = v/c$  and  $\gamma = 1/\sqrt{1-\beta^2}$ ) can be calculated using the relativistic Bethe-Bloch formula [14]:

$$-\left\langle \frac{dE}{dx}\right\rangle = \frac{4\pi}{m_e c^2} \cdot \frac{nz^2}{\beta^2} \cdot \left(\frac{e^2}{4\pi\varepsilon_0}\right)^2 \cdot \left[\ln\left(\frac{2m_e c^2 \beta^2}{I \cdot (1-\beta^2)}\right) - \beta^2\right],\tag{3.2}$$

with

$$n = \frac{N_A \cdot Z \cdot \rho}{A \cdot M_u},\tag{3.3}$$

where *v* is the speed of the particle, *z* its charge, *E* its energy, *n*, *I* and  $\rho$  respectively the electron density, the mean ionization potential and density of the material, *c* the speed of light,  $\epsilon_0$  the vacuum permittivity and *e* and  $m_e$  the charge and the mass of the electron, *Z* and *A* respectively the atomic number and the relative atomic mass of the material,  $N_A$  the Avogadro number and  $M_u$  the molar mass constant. Important to note is that the LET scales quadratically with the charge of the incident particle and increases with the electron density of the absorber material. The LET reaches a minimum around  $\beta \gamma = 3$ . Particles with this energy are called Minimum Ionizing Particles (MIPs). At low energies ( $\beta \gamma \leq 0.1$ ) the above equation is not valid any more and correction terms have to be

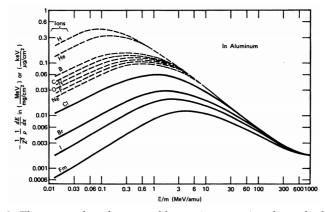

FIGURE 3.2: The energy loss for several heavy ions passing through aluminium.  $\rho$  is the density of aluminium, *Z* the ion's atomic number, and *m* is the mass of the ion expressed in atomic mass units [14].

added [10] to take into account atomic binding of electrons and the fact that the incident particle starts to carry atomic electrons with it. The latter reduces the incoming particle's effective charge and thus LET. The larger the charge of the incoming particle the more important this effect becomes and it becomes apparent at higher energies as shown in Figure 3.2. At high energies (1000  $\leq \beta\gamma$ ) radiative losses, e.g. due to bremsstrahlung, need to be taken into account.

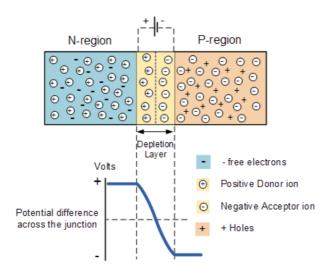

It is interesting to look at a few values and distributions for one specific material: silicon. Silicon is used as detection material, and is furthermore the main component of electronics. A good understanding of the energy deposition in silicon is thus important to understand both detection mechanisms and radiation damage.

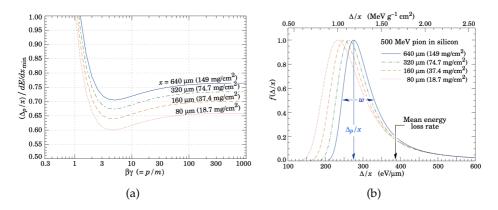

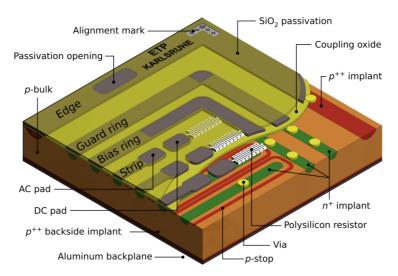

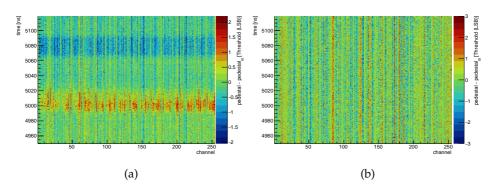

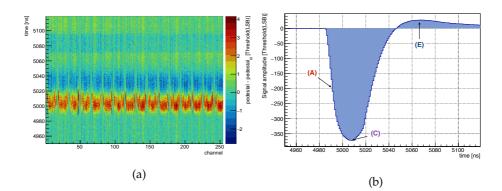

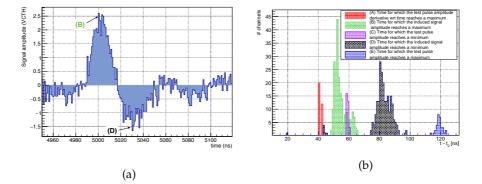

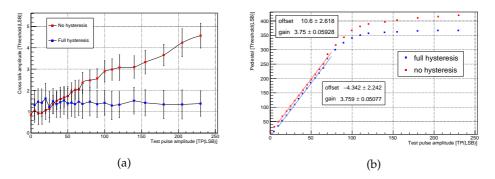

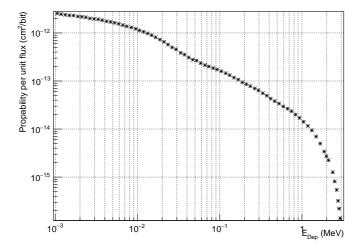

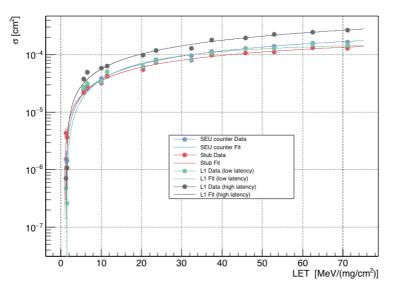

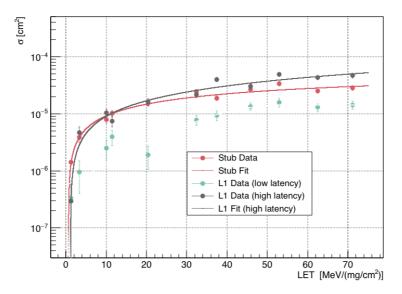

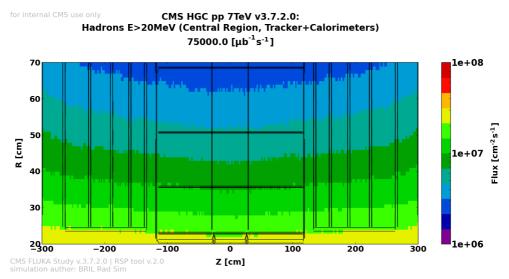

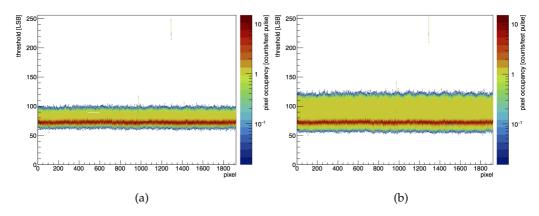

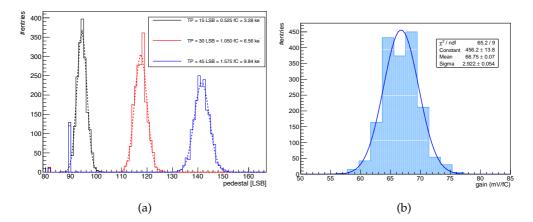

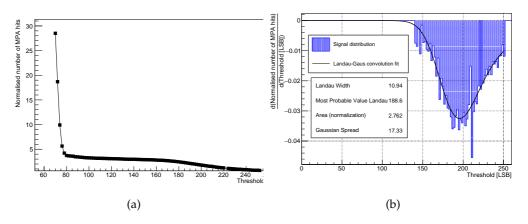

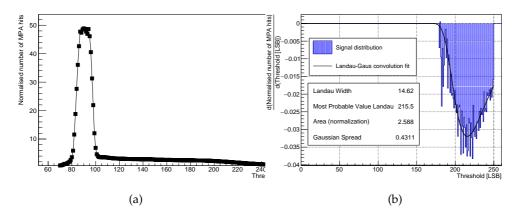

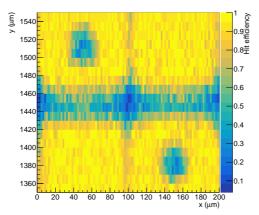

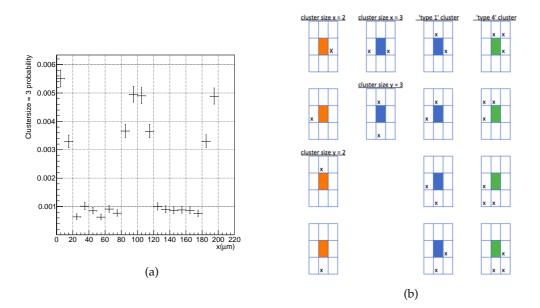

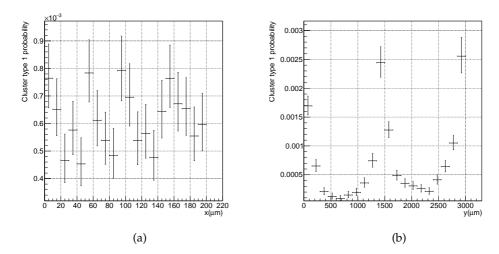

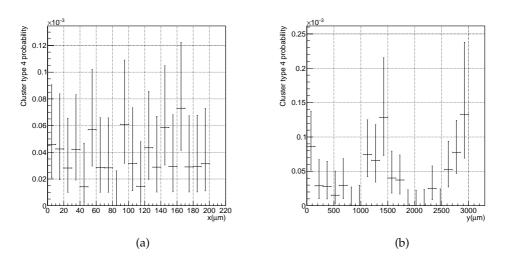

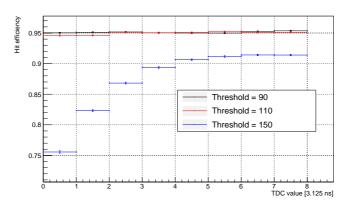

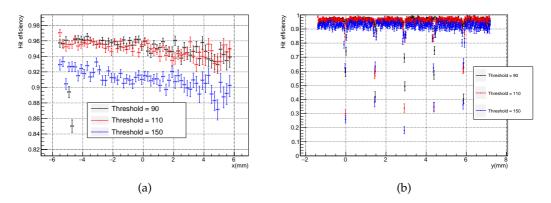

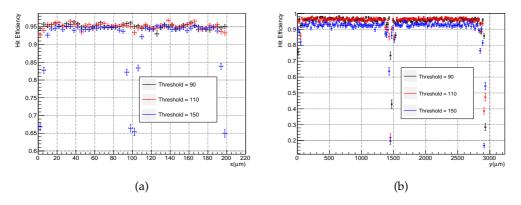

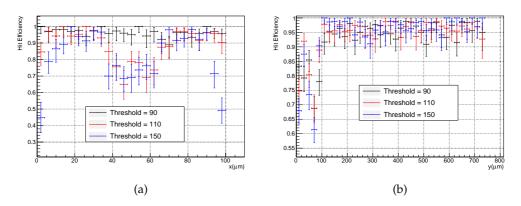

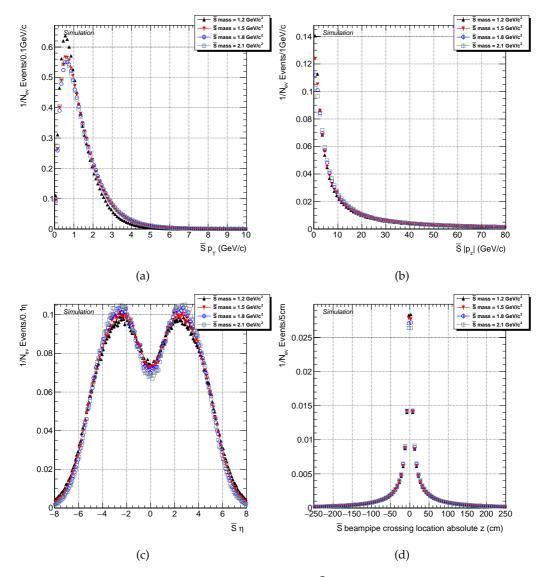

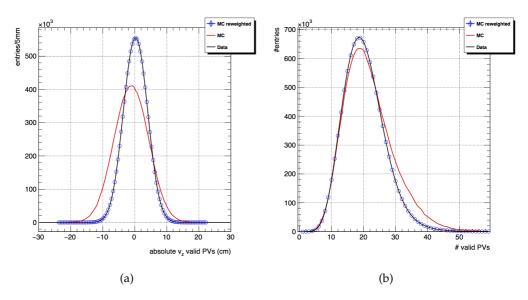

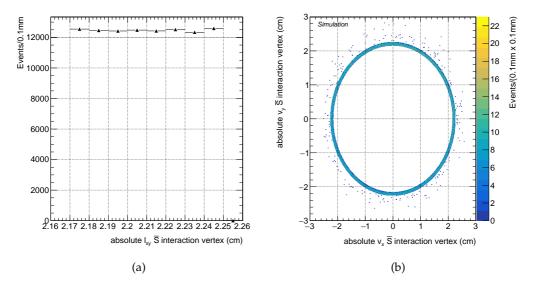

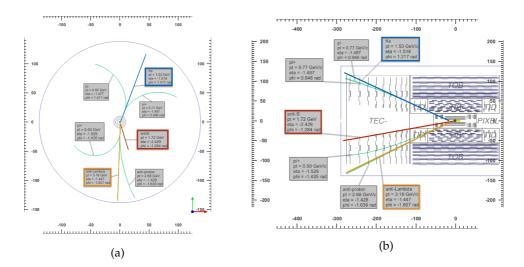

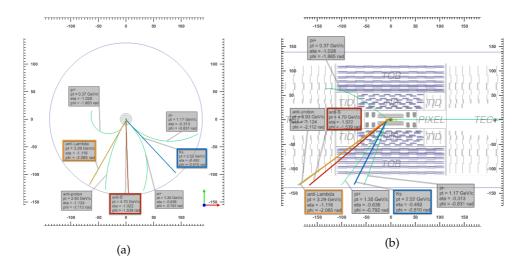

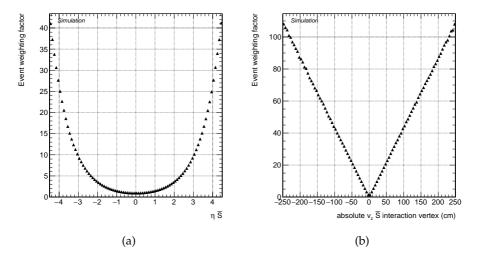

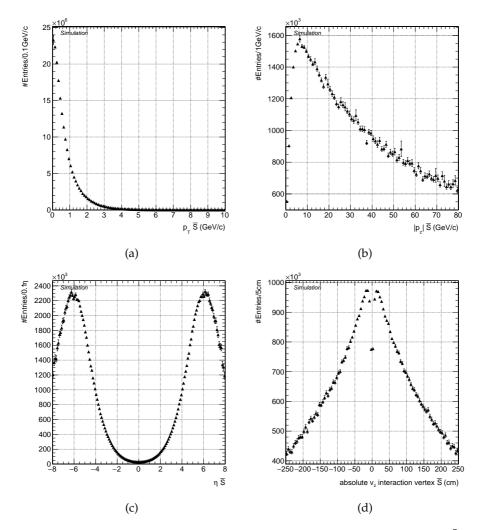

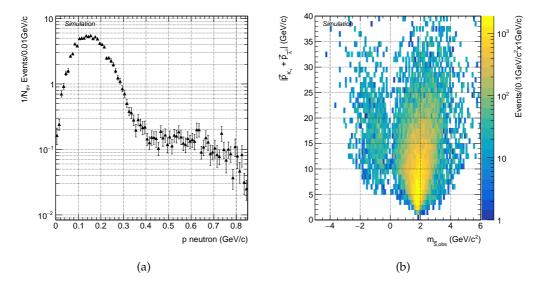

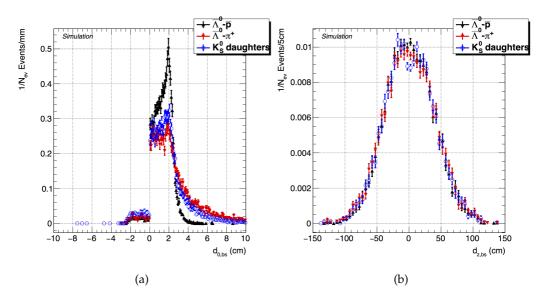

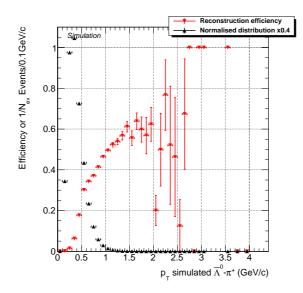

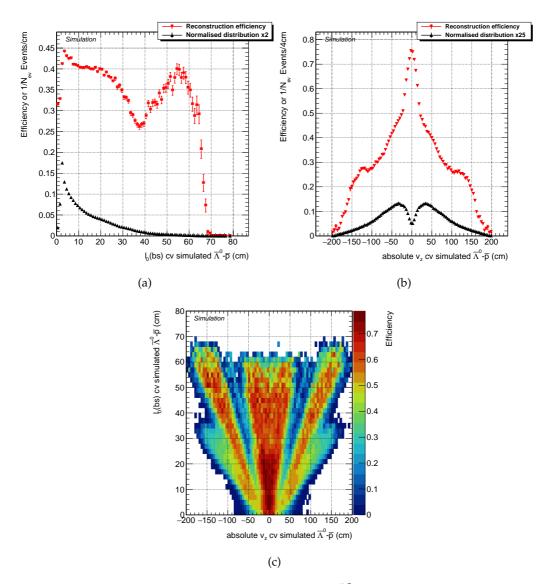

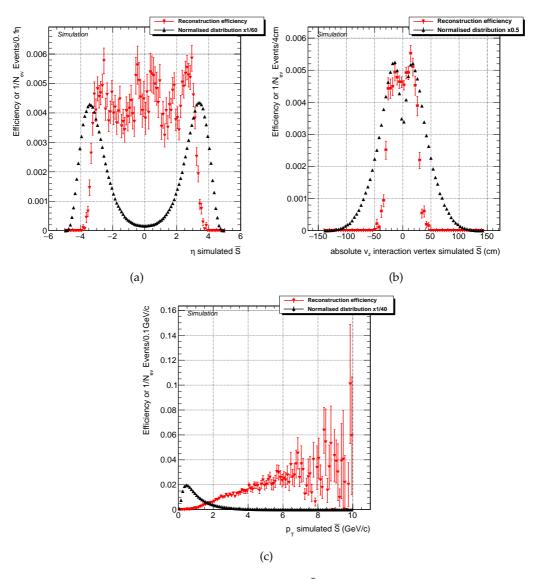

For high energy physics the tracking of charged particles with silicon detectors relies on the use of thin layers of silicon in which the particle deposits energy due to ionization, leaving behind electron-hole (e<sup>-</sup>h<sup>+</sup>) pairs. The average mean energy loss of a MIP in silicon is 388 eV/ $\mu$ m but corrections have to be taken into account for thin layers from which part of the secondaries can escape the volume [15]. These correction terms together with the evolution of the LET with the particle's energy are illustrated in Figure 3.3a. For a silicon sensor with a typical thickness of  $\approx 300 \ \mu$ m this gives a most probable value of 76 e<sup>-</sup>h<sup>+</sup>/ $\mu$ m for the number of electron-hole pairs formed along the path of the MIP (3.6 eV is required to generate an e<sup>-</sup>h<sup>+</sup> pair in silicon). The distribution of the deposited energy by a MIP in silicon is illustrated in Figure 3.3b and shows the typical skewed Landau distribution where the upper tails are due to  $\delta$ -rays.